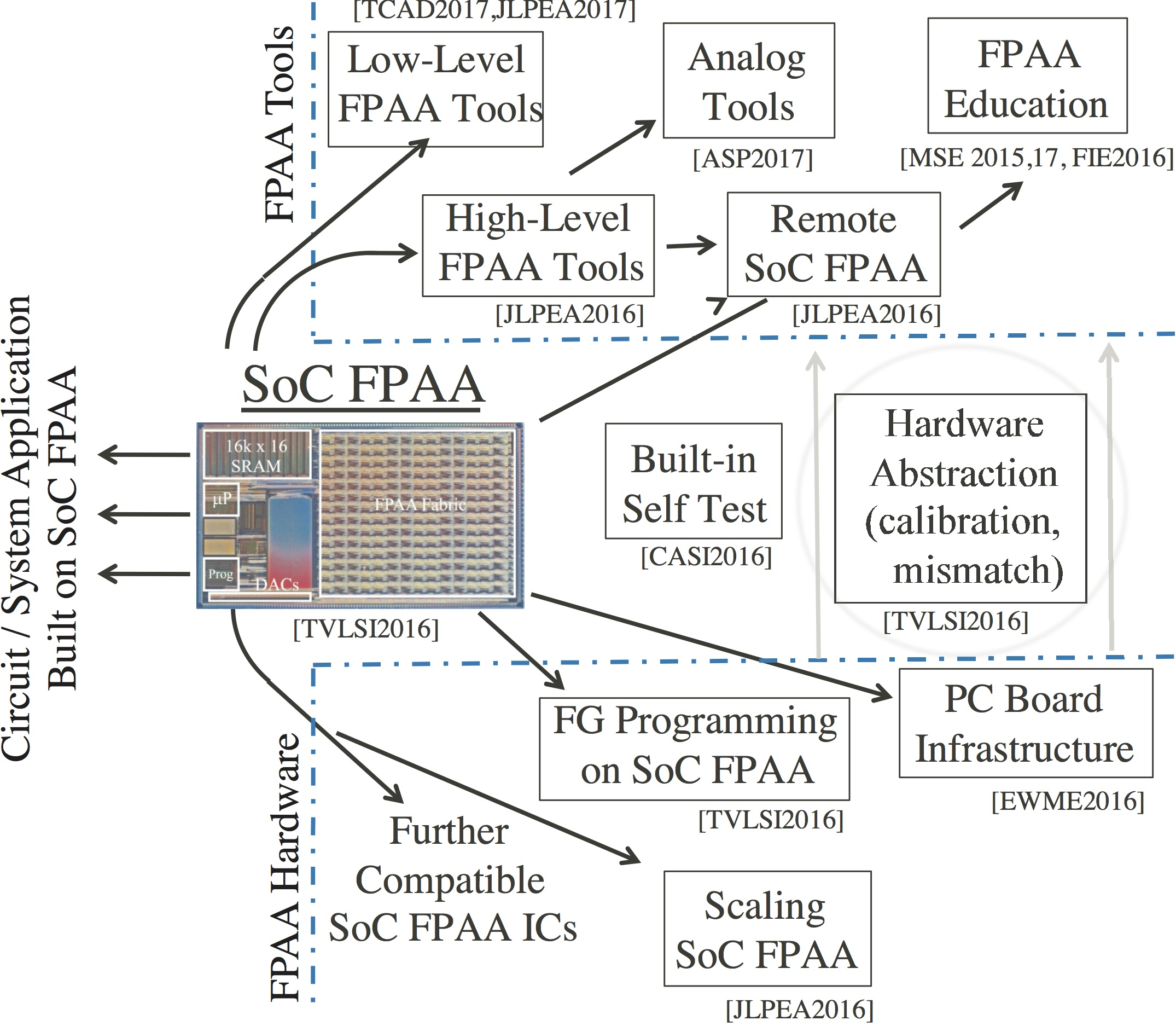

|

System on Chip (SoC) large-scale Field-Programmable Analog Array (FPAA)Lead Professor: Dr. Jennifer Hasler

[1] J. Hasler, "Large-Scale Field-Programmable Analog Arrays," Proceedings of IEEE, 2020. [2] S. George, S. Kim, S. Shah, et. al, "A Programmable and Configurable Mixed-Mode FPAA SOC,” IEEE Transactions on VLSI, vol. 24, no. 6, 2016. pp. 2253-2261. [3] M. Collins, J. Hasler, and S. George, "An Open-Source Toolset Enabling Analog–Digital–Software Codesign," Journal of Low Power Electronics Applications, January 2016. [4] J. Hasler and A. Natarajan, ``An Open-Source ToolSet for FPAA Design,'' WOSET, November 2020. [5] A. Natarajan and J. Hasler, ``Modeling, simulation and implementation of circuit elements in an open-source tool set on the FPAA,'' Analog Integrated Circiuits and Signal Processing, vol. 91, no. 1, January 2017, pp. 119-130. [6] J. Hasler, “Defining Analog Standard Cell Libraries for Mixed-Signal Computing enabled through Educational Directions,” IEEE ISCAS, May 2020. [7] S. Shah and J. Hasler, "Low Power Speech Detector On A FPAA," IEEE ISCAS , May 2017. [8] J. Hasler and S. Shah, "SoC FPAA Hardware Implementation of a VMM+WTA Embedded Learning Classifier," IEEE Trans. ECAS , March 2018. [9] S. Shah and J. Hasler, "VMM + WTA Embedded Classifiers Learning Algorithm implementable on SoC FPAA devices," IEEE Trans. ECAS , March 2018. [10] J. Hasler and S. Shah, "Learning for VMM + WTA Embedded Classifiers," GOMAC, 2016. [11] J. Hasler and S. Shah, "Enabling Embedded Learning and Classification Implemented on SoC FPAA Devices," [12] S. Shah, H. Treyin, O. T. Inan, and J. Hasler, “Reconfigurable analog classifier for knee-joint rehabilitation,” IEEE EMBC , August 2016. [13] S. Shah, C. N. Teague, O. T. Inan, and J. Hasler, “A proof-of-concept classifier for acoustic signals from the knee joint on an FPAA,” IEEE SENSORS, October 2016. [14] H. Toreyin, S. Shah, S. Hersek, Omer T. Inan, J. Hasler, "Proof-of-Concept Energy-Efficient and Real-Time Hemodynamic Feature Extraction from Bioimpedance Signals using a Mixed-Signal Field Programmable Analog Array," IEEE BHI 2017 , 2017. [15] H. Toreyin, S. Shah, and J. Hasler, “Real-Time Vital-Sign Monitoring in the Physical Domain on a Mixed-Signal Reconfigurable Platform,” IEEE Transactions on Biomedical Circuits and Systems, vol. 13, no. 6, December 2019. pp. 1690-1699. [16] J. Hasler and A. Natarajan, “Analog Soulions of Systems of Linear Equations on a Configurable Platform,” IEEE ISCAS, May 2020. [17] A. Natarajan and J. Hasler, “Built-in Self-Test of Vector Matrix Multipliers on a Reconfigurable Device,” IEEE ISCAS, May 2020. [17a] J. Hasler and S. Shah, "An SoC FPAA Based Programmable, Ladder-Filter Based, Linear-Phase Analog Filter," IEEE CAS I, vol. 68, no. 2, 2021. [18] J. Hasler, S. Kim, S. Shah, F. Adil, M. Collins, S. Koziol, and S. Nease, "Transforming Mixed-Signal Circuits Class through SoC FPAA IC, PCB, and Toolset," European Workshop on Microelectronics Education, Southampton, May 2016. [19] M. Collins, J. Hasler, and S. Shah, "An approach to using RASP tools in analog systems education," FIE , October 2016. [20] J. Hasler, A. Natarajan, S. Shah, and S. Kim, "SoC FPAA Immersed Junior Level Circuits Course," MSE , May 2017. [21] J. Hasler, "Circuit Implementations Teaching a Junior Level Circuits Course Utilizing the SoC FPAA," ISCAS,Florence, 2018. [22] J. Hasler, S. Shah, S. Kim, I. Lal, and M. Collins, "Remote FPAA System Setup Enabling Wide Accessibility of Configurable devices," Journal of Low Power Electronics Applications, June 2016. [23] J. Hasler, S. Shah, S. Kim, I. K. Lal, and M. Collins, "Remote System Setup Using Large-Scale Field Programmable Analog Arrays (FPAA) to Enabling Wide Accessibility of Configurable Devices," Journal of Low Power Electroncs Applications, vol. 6, no. 14, 2016, pp. 1-17. [24] S. Kim, J. Hasler, and S. George, "Integrated Floating-Gate Programming Environment for System-Level Ics," IEEE Transactions on VLSI , 2016. [25] J. Hasler, S. Kim, and F. Adil, "Scaling Floating-Gate Devices Predicting Behavior for Programmable and Configurable Circuits and Systems," Journal of Low Power Electroncs Applications, vol. 6, no. 13, 2016, pp. 1-19. [26] J. Hasler andi H. Wang, “A Fine-Grain FPAA fabric for RF+Baseband,” GOMAC, 2015. [27] S. Shah and J. Hasler, "Tuning of Multiple Parameters With a BIST System," IEEE CAS I, vol. 64, no. 7, July 2017, pp. 1772-1780. [28] S. Kim, S. Shah, J. Hasler, "Floating-Gate FPAA Calibration for Automated Analog Circuit and System Design," IEEE ISCAS , May 2017. [29] S. Kim, S. Shah, and J. Hasler, "Calibration of Floating-Gate SoC FPAA System," IEEE Transactions on VLSI , 2017. [30] S. Shah, H. Toreyin, J. Hasler, A. Natarajan ``Temperature Sensitivity and Compensation On A Reconfigurable Platform,'' IEEE Transactions on VLSI , Vol. 26, no. 3, March 2018. pp. 604-607. [31] S. Shah, H. Toreyin, J. Hasler, and A. Natarajan, ``Models and Techniques For Temperature Robust Systems On A Reconfigurable Platform,'' Journal of Low Power Electronics Applications, vol. 7, no. 21, August 2017. pp. 1-14. [32] J. Hasler, "Security Implications for Ultra-Low Power Configurable Analog and Mixed Mode SoC Systems," [33] J. Hasler and S. Shah, "Reconfigurable Analog PDE computation for Baseband and RF Computation," GOMAC , March 2017. [34] Electronic Product Magazine, March 21, 2016. "New analog chip uses 1,000 times less electrical power (and can be built a hundred times smaller) than comparable digital devices" [35] http://www.rh.gatech.edu/news/508791/configurable-analog-chip-computes-1000-times-less-power-digital |