# A Real-Time Vital-Sign Monitoring in the Physical Domain on a Mixed-Signal Reconfigurable Platform

Sahil Shah, Student Member, IEEE, Hakan Töreyin, Member, IEEE, Cihan Berk Güngör, Student Member, IEEE, and Jennifer Hasler, Senior Member, IEEE

Abstract—This work presents a mixed-signal physical-computation-electronics for monitoring three vital signs; namely heart rate, blood pressure, and blood oxygen saturation; from electrocardiography, arterial blood pressure, and photoplethysmography signals in real-time. The computational circuits are implemented on a reconfigurable and programmable signal-processing platform, namely field-programmable analog array (FPAA). The design leverages the core enabling technology of FPAA, namely floatinggate CMOS devices, and an on-chip low-power microcontroller to achieve energy-efficiency while not compromising accuracy. The custom physical-computation-electronics operating in CMOS subthreshold region, performs low-level (i.e., physiologically-relevant feature extraction) and high-level (i.e., detecting arrhythmia) signal processing in an energy-efficient manner. The on-chip microcontroller is used (1) in the programming mode for controlling the charge storage at the analog-memory elements to introduce patient-dependency into the system and (2) in the run mode to quantify the vital signs. The system has been validated against digital computation results from MATLAB using datasets collected from three healthy subjects and datasets from the MIT/BIH open source database. Based on all recordings in the MIT/BIH database, ECG R-peak detection sensitivity is 94.2%. The processor detects arrhythmia in three MIT/BIH recordings with an average sensitivity of 96.2%. The cardiac processor achieves an average percentage mean error bounded by 3.75%, 6.27%, and 7.3% for R-R duration, systolic blood pressure, and oxygen saturation level calculations; respectively. The power consumption of the ECG, blood-pressure and photo-plethysmography processing circuitry are 126 nW, 251 nW and 1.44  $\mu$ W respectively in a 350 nm process. Overall, the cardiac processor consumes 1.82  $\mu$ W.

Index Terms—Energy-efficient cardiac signal processing, real-time physical signal processing, wearable sensor nodes.

Manuscript received July 8, 2019; revised September 23, 2019; accepted October 22, 2019. Date of publication October 28, 2019; date of current version December 31, 2019. The paper was recommended by Associate Editor B. Gosselin. (*Corresponding author: Hakan Töreyin.*)

- S. Shah is with the California Institute of Technology, Pasadena, CA 92115 USA (e-mail: sshah389@caltech.edu).

- H. Töreyin is with the Department of Electrical and Computer Engineering, San Diego State University, San Diego, CA 92182 USA (e-mail: https://doi.org/10.1007/j.chm.edu.edu).

- C. B. Güngör is with the Department of Electrical and Computer Engineering, University of California San Diego, La Jolla, CA 92093 USA and also with San Diego State University, San Diego, CA 92182 USA (e-mail: cgungor@eng.ucsd.edu).

- J. Hasler is with the School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, GA 30308 USA (e-mail: jennifer.hasler@ece.gatech.edu).

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TBCAS.2019.2949778

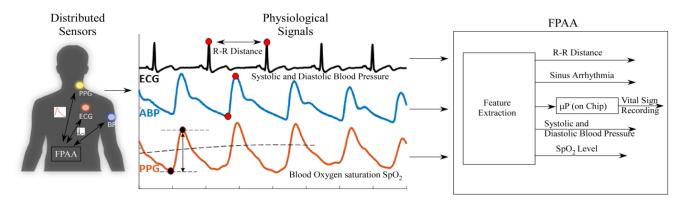

Fig. 1. This study presents design and results of energy-efficient physical computation electronics introducing real-time local intelligence to distributed cardiac sensors. Focus is given to ECG, ABP, and PPG signal processing. Energy-efficient and real-time vital sign monitoring, physiologically-relevant data compression, and cardiac health warning generation have been demonstrated on a mixed-signal reconfigurable FPAA platform.

# I. MOTIVATION FOR REAL-TIME AND ENERGY-EFFICIENT CARDIAC SIGNAL PROCESSING

FEART DISEASE (HD) is the primary reason for death in the U.S. and health care expenditure for HD imposes the largest burden on the total national health spending [1]. Furthermore, it is expected that by 2035, the percentage of the U.S. population having at least one HD will rise to 45%. Early diagnosis, and timely management of HD can potentially lower risk of complications, thus improving quality-of-life [1]– [4]. However, current HD diagnosis approach is reactive and therefore inappropriate for early diagnosis: Only after symptoms occur patients visit the clinic, where expensive procedures are used for diagnosis. In contrast, a proactive approach, where people are ubiquitously monitored at home for timely detection of signs of abnormalities before serious symptoms manifest, can increase the rate of early diagnosis. Such proactive approach can also facilitate treatment being tuned to changes in patients' physiology, thereby potentially increasing treatment success rates and reducing the frequency of visits to the clinic as well as the healthcare costs.

Datasets collected from human-subject studies have shown that several critical hemodynamics and vital sign variables can be extracted from electrocardiography (ECG) [5], arterial blood pressure (ABP) [6], and photoplethysmography (PPG) [7] signals. Accordingly, several research groups and companies have developed wearable/implantable systems to capture and analyze those signals for cardiovascular health-assessment outside the clinic [9]–[15]. Majority of these devices consist of a (network of) sensor(s) collecting analog physiological data, which is digitized by a microprocessor ( $\mu$ P) for detailed offline analysis. But a  $\mu$ P consumes milliamperes of current and due

1932-4545 © 2019 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

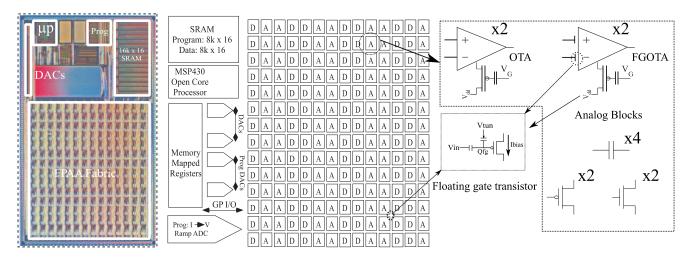

Fig. 2. Schematic and chip die of the Field Programmable Analog Array. The FPAA fabric consist of CABs and CLBs. These elements are programmed using the microprocessor and programming infrastructure. CAB element which are used in this work are also shown here. Interconnects, biasing of the OTA and inputs to the FGOTA are composed of Floating Gate (FG) transistors. The die photo of the FPAA SoC, fabricated in 350 nm process, is also shown and has a dimension of 12 mm × 7 mm. An MSP430 micro-processor is also synthesized on the same die. The FPAA fabric and contents are from [8].

to battery-life considerations, it is impractical to use  $\mu P$  for continuous processing of signals collected by sensor-nodes distributed across the body. Alternatively, a central processing unit with high computational power might receive and analyze the physiological data collected at different nodes. In such a scenario however, transmission of large datasets to the central processor necessitates high-throughput, and thus potentially power-hungry communication channels.

A potential solution to the aforementioned problem would be localized energy-efficient computation-nodes (Fig. 1). In a network with distributed and low-power computational capabilities, salient information could be extracted from the raw signals directly at the sensor site, thus significantly alleviating the burdens on the communication channel as well as the central signal processor. It should be noted that, in a body sensor network, physiological parameters of interest might change depending on the context. For instance, it is expected that the type and/or number of important physiological parameters during an exercise session (e.g., muscle activity) would be different than those during the activities of daily living. Therefore, a localized computation solution should offer adaptability to those changes to maximize the efficiency of resource-usage.

In this work, we present a proof-of-concept energy-efficient cardiac processor for analyzing cardiac signals in real-time. The focus of the paper is to demonstrate that custom analog-signal-processing algorithms implemented on a reconfigurable and programmable Field-Programmable Analog Array (FPAA) achieve superior energy-efficiency and resource usage performances compared to digital reconfigurable or programmable platforms. The energy efficiency is achieved because of (i) the design simplicity when implementing the signal processing functions using physical principles and (ii) facilitating the CMOS subthreshold region. The FPAA enables programmability and reconfigurability by leveraging Floating-Gate (FG) MOS devices.

This paper is organized as follows. In the following section, an overview of the FPAA platform, the cardiac signals of interest, and methods for evaluating the computation electronics are

presented. Details of the electronics design and measurement results are presented in Section III, which is followed by a discussion in Section IV. The paper is concluded in Section V.

#### II. METHODS: FPAAS FOR ANALYZING CARDIAC SIGNALS

#### A. FPAA: A Reconfigurable Mixed-Signal SoC

There has been a growing interest in FPAA as a large-scale mixed-signal SoC. Similar to a Field Programmable Gate Array (FPGA) an FPAA makes prototyping mixed-signal systems cost effective and shortening the test cycles [16], [17]. FG-based FPAAs [18]–[23] offer the required reconfigurability and programmability when implementing large analog systems typically suffering from mismatch and process variations [24], [25].

The FPAA is shown in Fig. 2 and described in detail in [8]. It has both analog and digital blocks; namely Computational Analog Block (CAB) and Computational Logic Block (CLB); respectively. FPAA used in this work comprises of 98 CABs and 98 CLBs. These computational blocks are connected using Manhattan style routing composed of Connection (C) and Switch (S) blocks. These interconnect switches, which enable seamless connection between analog and digital blocks, are composed of nonvolatile FG transistors, show in Fig. 2., which are programmed using hot-electron injection and globally erased using Fowler-Nordheim tunneling. The programming infrastructure used for tuning and programming the FG switches is composed of 7-bit DACs and a 14-bit ADC and are controlled using an open source MSP430 microprocessor. The microprocessor has a controllable frequency of 0-50 MHz and is synthesized on the same die as the FPAA fabric. An  $8k \times 16$  bit SRAM is used to store the program to be executed by the microprocessor and a separate data memory of  $8k \times 16$  bit is also present. As a part of the infrastructure there are sixteen 7-bit DACs for analog inputs to the FPAA fabric. The 14-bit ramp ADC, which is primarily used for measuring the current of a FG, can also be configured to digitize analog computation outputs.

Fig. 3. Physiological signals and their analysis on the reconfigurable cardiac processor. Electrocardiogram (ECG), arterial blood pressure (ABP), and photoplethysmography (PPG) signal can be used for extracting important features and vital information are shown. Analog processing enables computation without using ADC, and hence significantly lower-power compared to the digital implementation of the algorithms. This is significant when such devices are used for continuous monitoring. The block diagram of the mixed-signal cardiac signal processor designed and implemented on an FPAA is also shown in the figure. The feature extraction and abnormality detection are performed in the physical domain, whereas vital sign value calculation is performed using the on-chip microprocessor.

Basic elements of a CAB, particularly the elements used in this work are shown in Fig. 2. CAB elements are connected using local interconnects and the system use global routing while interconnecting to a different CAB. A CAB contains multiple Operational Transconductance Amplifiers (OTA) with the ability to select between wide linear range and high gain amplifier. Current bias of the OTA as well as the DC bias of the FGOTA is set using an FG transistor as shown in Fig. 2. Similar to the interconnect switches, these FG transistors are programmed by a charge  $Q_{FG}$  using hot-electron injection and erased using Fowler-Nordheim tunneling. Unlike the interconnect switches, these FG transistors are programmed precisely to achieve the necessary biasing current  $(I_{\text{bias}})$  [26]. The programming infrastructure enables programming the bias current values from 5 pA to 10  $\mu$ A, and thus enabling calibration and tuning of the cardiac processor.

## B. Overview of the Cardiac Signals and Features Critical for Vital Sign Calculation

The cardiac processor receives ECG, ABP, and PPG signals to compute R-R distance, systolic/diastolic blood pressure, and blood oxygen-saturation level (Fig. 3). In an ECG signal, R-wave, which is the global maxima point in a heartbeat, is critical for calculating the R-R distance, and therefore heart rate. In an arterial blood pressure (ABP) waveform, the maxima and minima points correspond to the systolic (SBP) and diastolic (DBP) blood pressure, respectively. Oxygen saturation (SpO<sub>2</sub>) can be calculated from two PPG signals at different wavelengths by calculating their perfusion index ratio. In this study, we use two commonly-used wavelengths, red and infrared (IR). The perfusion index of a PPG signal is calculated as the ratio of peak-to-peak PPG variations at different wavelengths respectively normalized by their corresponding dc levels.

### C. Methods for Cardiac Signal Processor Validation

1) Physiological Datasets: The performance of the R-peak detection algorithm has been evaluated using all recordings in

the MIT/BIH arrhythmia database [27], [28]. In-case of, detection of R-R distance, SBP and DBP, and SpO<sub>2</sub> by the processor has been validated using datasets collected from three healthy adults. All measurements were approved by the Georgia Institute of Technology Institutional Review Board (IRB). The ECG dataset was collected using a wireless BioNomadix ECG module (Biopac Systems Inc., Goleta, CA). The ABP dataset was collected using a Finapres device (Finapres Medical Systems, Amsterdam, Netherlands) utilizing volume clamping technique for non-invasive and continuous blood pressure monitoring. The red and IR PPG dataset was collected using an AFE4400SPO2EVM pulse-oximeter evaluation-module (Texas Instruments, Dallas, TX). All signals were collected using a sampling rate of 2 kSps per channel. We followed a measurement protocol consisting of rest, handgrip exercise, and deep breathing phases and creating perturbations in heart rate (HR) and BP. During measurements, the subjects were in standing position.

For validation of the sinus arrhythmia warning generation circuitry, 10 minutes ECG recordings from three different adults (recordings 114, 210, and 214) in the MIT/BIH database have been used [27], [28].

- 2) R-Wave Detection Algorithm Validation: The robustness of the R-wave detection algorithm has been validated using the simulation environment of the FPAA [29]. The environment facilitates an open source clone of MATLAB/SIMULINK, namely SCILAB/XCOS, and provides a graphical interface enabling simulations, rapid prototyping, and calibration. For all 48 ECG recordings of the MIT/BIH arrhythmia database, the first channels are used in this study. Each recording is fed to the simulation environment following digital signal conditioning to fit the signal into input rails of the processor. The simulation outputs are compared against the annotations in the database to extract the sensitivity (Se) using Se = TP/(TP + FN), where TP and FN are respectively true positive and false negative values.

- 3) Cardiac Signal Processor Validation Setup on FPAA: For validation purposes, the waveforms have been streamed on to the FPAA using a 14-bit DAC. In an ultimate BSN cardiac sensing node scenario, sensors could be directly interfaced with the

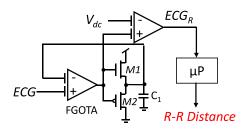

Fig. 4. ECG R-wave features are detected by a hysteretic differentiator followed by a voltage comparator. The output of the voltage comparator, which is a train of pulses, is fed to the microprocessor for finding the R-R distance. Consistency is observed in the exemplary waveforms displaying the R-R distance calculated by the on-chip microprocessor using the features detected by the circuit implemented on the FPAA fabric and MATLAB using the features found by MATLAB.

FPAA using either a low-noise amplifier or capacitively coupled amplifiers, depending on the type of the sensor/transducer.

For cardiac feature extraction accuracy assessment, the cardiac processor outputs have been compared with the outputs of digital signal processing algorithms implemented on MATLAB. Sinus arrhythmia detection performance of the processor has been evaluated through comparison with the arrhythmia events annotated on each ECG recordings.

#### III. RECONFIGURABLE CARDIAC PROCESSOR

#### A. Feature Extraction from Physiological Data for Vital Signs

1) ECG R-Wave Detection: The R-wave of a heartbeat, which is critical for heart rate calculation, is preceded and followed by points where the magnitude of the first derivative of the ECG signal is maximum. Therefore, the R-wave detection circuitry is designed to detect the sharp and large changes in the slope while suppressing the small changes such as noise. Accordingly, the R-wave detector algorithm is designed as a hysteretic differentiator with a time-constant set by the transconductance of an operational transconductance amplifier (OTA) and a load capacitance,  $C_1$  (Fig. 4). FGOTA has an increased linearity as compared to a traditional non-FGOTA at the expense of gain [30]. The increased linearity of the FGOTA follows from the differential current given by the following equation:

$$I \text{ out} = I_{\text{bias}} \tanh \left( \kappa \frac{C_{\text{in}}}{C_T} \frac{V_{\text{in}1} - V_{\text{in}2} + V_{\text{offset}}}{2U_T} \right) \tag{1}$$

where  $V_{\rm in1}$  and  $V_{\rm in2}$  are differential input voltage of the FGOTA and  $V_{\rm offset}$  is mismatch due to threshold voltage mismatch and FG charge programmed,  $C_{\rm in}$  is input capacitor to the FGOTA and  $C_T$  is total capacitance at the FG node,  $\kappa$  is the fractional change in surface potential with respect to change in gate voltage, and  $U_T$  is thermal voltage which is approximately equal to 25 mV at room temperature. The additional term  $C_{\rm in}/C_T$ , the ratio of input capacitance to the total capacitance at the input of the differential FGOTA, results in increased linearity over traditional non-FG OTA. Linearity of the FGOTA can be increased by increasing the total capacitance  $C_T$  [31]. The FGOTA is used as part of the hysteretic differentiator as seen in Fig. 4. Hysteretic differentiator's output is responsive only to major changes in sign

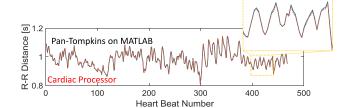

Fig. 5. The R-R distance calculated by the cardiac processor and Pan-Tompkins implementation on MATLAB match. The exemplary data corresponds to ECG data from a healthy subject.

of the derivative of the input voltage. Additionally, by changing the  $g_m$  ( $I_{\text{bias}}$ ) of the FGOTA, noise immunity can be further enhanced by making  $V_{C1}$ , the voltage of  $C_1$  in Fig. 4, to lag even further behind the input [32]. For small signals, the output of the hysteric differentiator in Fig. 4 is governed by:

$$C_{\text{out}} * \frac{dV_{\text{out}}}{dt} = G_m \times (V_{\text{ECG}} - V_{C1})$$

(2)

where  $G_m$  is the transconductance of the FGOTA given by  $(I_{\text{bias}} * \kappa * (C_{\text{in}}/C_T)/(2 * U_T)$ . The time constant in (2), given by  $\tau = C_{\rm out}/G_m$ , is selected such that high-frequency noise above 50 Hz is suppressed specifically the 60-Hz noise. Using the parameters extracted in [33]  $\kappa_*(C_{\rm in}/C_T) = 0.48$  and  $C_{\text{out}} = 1 \text{ pF we get } I_{\text{bias}} \text{ of } 33 \text{ pA}.$  This value was then used as the basis for the Built-In-Self-Test (BIST) which tuned the biasing current to 0.1 nA to obtain the specified 50 Hz bandwidth. The BIST architecture is similar to the one described in [34] and it takes into account the mismatch that arises from indirect programming of FG [26], differences in the load-capacitance and other mismatches that arise in CMOS process. The capacitor (C1) shown in Fig. 4 is local routing capacitance and has a value of 160 fF. An FGOTA comparator converts the differentiator output into clock pulses fed to the microcontroller for calculation of the HR value. The FGOTA also allows us to precisely program the offset of the OTA and hence the comparator threshold could be configured depending on the subject. R-R distance calculated using the comparator outputs, ECGR, from ECG recordings of one of the healthy subjects, match with those calculated using the R-waves detected by the MATLAB implementation of the Pan-Tompkins algorithm [35] (Fig. 5). The on-chip  $\mu P$  counts the time between the rising edges of the  $ECG_R$  pulses, whereas the R-R distances of the Pan-Tompkins output are calculated using the R-wave peak points. Accordingly, small (<1 ms) differences occur between the two data (close-up view in Fig. 5). The two results exhibit a Pearson correlation coefficient of 0.99.

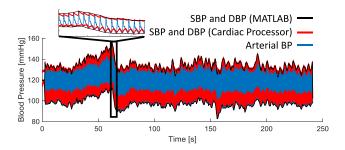

2) ABP Feature Extraction: The SBP and DBP values; which are the maximum and minimum values of the continuous ABP waveform, respectively; are detected by an envelope tracking circuitry. The operation of the positive peak detection circuitry (Fig. 6) is as follows. When the input signal is greater than the output (i.e., ABP signal is increasing), the NMOS controlled by the FGOTA output charges the load capacitor,  $C_{L1}$ , thereby causing the output to follow the input. When the input is less than the output, the NMOS controlled by a fixed bias voltage discharges the  $C_{L1}$  at a discharge rate given by  $I_1/C_{L1}$ , where

Fig. 6. SBP and DBP are detected from the ABP waveform via maximum and minimum detection circuitry, respectively.

Fig. 7. Exemplary SBP and DBP waveforms obtained from the ABP of a healthy subject are shown. The SBP and DBP values obtained by MATLAB are also provided for comparison.

$I_1$  is dependent on current through M1 and M2. We empirically selected the  $V_{\rm bias}$  value for a maximum detector to limit the discharge rate such that the maximum value is held almost constant between successive heart beats, which can take as long as 1 sec (60 bpm). Likewise, we empirically selected bias currents for the FGOTAs such that the capacitor charge rate is sufficiently large to charge  $C_{L1}$  and track the input signal in less than 50 ms when the next heart beat arrives. The minimum peak detection circuitry differs from the positive peak detection circuitry by using PMOS instead of NMOS devices for generating the  $C_{L2}$ current. SBP and DBP signals obtained by the processor and MATLAB from an ABP waveform are presented in Fig. 7. The capacitors ( $C_{L1}$  and  $C_{L2}$ ) and devices ( $M_1$  in SBP circuitry and M<sub>2</sub> in DBP circuitry) affect the discharge rate. The bias voltage,  $V_{\rm bias}$ , can be tuned to compensate for potential process variations in these elements. Similarly, by tuning the FGOTA bias current, potential process variations can be compensated to ensure the output can be ensured to follow the input before the maximum (SBP) and minimum (DBP) peaks.

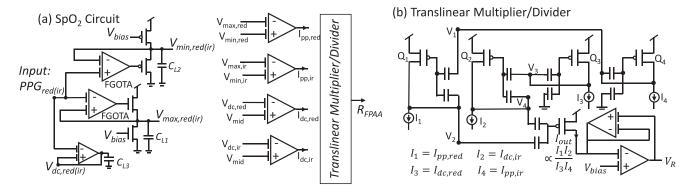

3) PPG Feature Extraction: For monitoring the  $SpO_2$ , the cardiac processor calculates the ratio (R) of the perfusion indices (i.e., ratio of the pulsatile blood flow signal to static blood flow) of PPG waveforms at red and infrared wavelengths [36].

The perfusion-index-ratio extraction block consists of circuitry detecting the 1<sup>st</sup> order features, namely the peak-to-peak and dc values of red and infrared wavelength PPG signals; followed by an arithmetic operation circuitry for calculating the ratio of the perfusion indices (i.e.,  $R = \frac{V_{pp,red}}{V_{dc,red}} / \frac{V_{pp,ir}}{V_{dc,ir}}$ ) of red and infrared wavelength PPG signals. Peak-to-peak detection is achieved using the envelope detection circuitry described in the ABP feature extraction section. We follow the approach described in Section III.A.2 for the bias selection of the PPG envelope detection circuitry. The dc values of the PPG signals

are detected through a low-pass-filter (LPF) implemented as a  $G_m$ -C stage with a time constant set to  $f_{-3dB}=300~\mathrm{mHz}$  by the transconductance of an FGOTA and a load capacitance (Fig. 8(a)). The time constants are tuned using a BIST method [34]. The BIST is used to automatically tune parameters to the desired values (e.g., the time constant for the LPF). The two-step calibration procedure used for an FPAA is detailed in Section IV. The time-constant is calculated using models simulated in MATLAB to achieve desired performance. The inputs to the next stage are output currents of wide input-linear-range ( $\sim$ 1.5 V) FGOTAs fed by the voltage outputs of the envelope detection and LPF circuitry.

For ease of computation and therefore reduced design complexity, calculation of perfusion indices as well as their ratio is achieved in the analog domain using current signals. This is important from the standpoint of real-time monitoring system where the continuous use of analog to digital converter (ADC) will increase the power consumption. The overall calculation is reduced into a single translinear multiplier/divider circuitry using multiple input translinear elements (Fig. 8(b)), where the output current, Iout, is dependent to I1-to-I4 through:

$$I_{\text{out}} \propto (I_1 I_2) / (I_3 I_4)$$

. (3)

The relationship in (3) follows from the drain current for FG pMOS in subthreshold regime operated in saturation, and the fact that current is mirrored [37], [38]. The following equations illustrates the relationship between input current and output currents:

$$I_{\text{out}} = I_{th} * e^{\frac{\kappa(V_{DD} - w_{V2} - w_{V4} - V_{th})}{U_T}}$$

(4)

$$I_{\text{out}} \propto e^{\frac{-w_1 V_2}{U_T}} * e^{\frac{-w_1 V_4}{U_T}}$$

(5)

where w1 is the product of  $\kappa$  and FG weight w. V2 and V4 are as shown in Fig. 8(b) and can be replaced in terms of current I1, I2, I3 and I4. The relation for an FG drain current with respect to FG voltages for Q1 is given as follows:

$$V_2 \propto -\ln\left(I_1\right) \frac{U_T}{w_1} - V_1 \tag{6}$$

Similar relation can be written for Q2, Q3 and Q4 transistors in Fig. 8. Replacing equation (6) in (5) we get

$$I_{\text{out}} \propto e^{\frac{-w_1}{U_T} \left(-\ln(I_1)\frac{U_T}{w_1} + \ln(I_4)\frac{U_T}{w_1}\right)} * e^{\frac{-w_1}{U_T} \left(-\ln(I_2)\frac{U_T}{w_1} + \ln(I_3)\frac{U_T}{w_1}\right)}$$

(7)

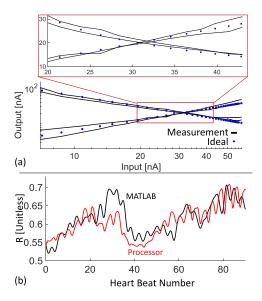

Reducing the above equation, we get the relation in (3). The above relation and the linearity hold true only if the charges programmed on the FGs are equal and the FGs are matched. The  $I_{\rm out}$  is converted into voltage,  $V_{\rm out}$ , at a transimpedance stage implemented as an OTA with an FGOTA-buffer feedback resistance (Fig. 8(b)). Linearity of the translinear elements and comparison of processor output,  $V_R$ , and digital MATLAB calculations of the perfusion-index-ratio are presented in Fig. 9.

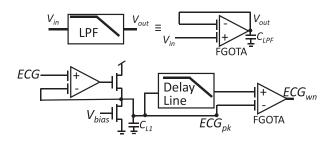

## B. Sinus Arrhythmia Detection From ECG

Sinus arrhythmia manifests itself as irregular R-R intervals, resulting in prolonged R-R intervals for some heart beats [39]. In this proof-of-concept algorithm, we aim to detect abnormal

Fig. 8. (a)  $SpO_2$  calculation circuitry. To calculate the peak-to-peak and dc value parameters required to calculate the perfusion indices of red and infrared wavelength PPG signals, max-min detect and  $G_mC$  LPF stages are designed, respectively. The voltage outputs are converted into current at FGOTAs to achieve the (b) perfusion index ratio operation in the current domain using a translinear current multiplier/divider implemented using multiple-input translinear elements (MITEs).

Fig. 9. (a) Measurement results for the translinear circuit output  $(I_{\rm out})$  vs. input  $(I_1)$  current for two  $I_2$  and two  $I_4$  values are presented. During operation,  $I_1-I_4$  are limited to 20 nA - 43 nA, where the circuit is linear. (b) The perfusion-index-ratio waveforms obtained by the cardiac processor and MATLAB. The smoothed waveforms follow similar trends and have similar peaks and valleys.

increases in R-R intervals. To detect such irregularity, the R-R interval is first time-integrated using a peak-detector circuitry (Fig. 10). To a first order approximation, charge leakage of the load capacitor can be modelled as a constant current source reducing the  $C_{L1}$  potential by an amount proportional to the R-R interval between successive peaks. The output of the peak-detector is compared with an adaptive threshold at a comparator to generate a warning pulse in the event of abnormally long R-R interval. The adaptive threshold value is selected such that false positives during normal gradual R-R interval increases (e.g., drops in the HR following deep breathing or exercise) are prevented while abrupt increases (occurring within < 1 s) in the R-R interval are detected as arrhythmia events. The adaptive threshold is created as the one second delayed and smoothed

Fig. 10. Sinus arrhythmia detection circuitry. The maxima waveform of an ECG signal, which is tracked by a peak detection circuitry, is fed to a comparator. The threshold for the comparator is a delayed version of the ECG maxima waveform.

version of  $ECG_{pk}$  signal. The delay network consists of eight cascaded LPF  $G_mC$  stages (Fig. 10).

Notably, arrhythmia events can be detected using the ECG-R wave circuit (Fig. 4) in conjunction with the microprocessor. In that case, it would require several registers to store previous set of values and digital logic to detect sudden changes in R-R distance. On the contrary, the proposed circuit in Fig. 10 enables detection of arrhythmia without having to use a digital counter, the registers for storing previous set of R-R distance, or logic circuitry to detect the sudden change in those values.

#### C. Vital Sign Data Logging

The on-chip low-power MSP430 microprocessor with an energy efficiency of 216  $\mu$ W/MHz is used to calculate and log some of the physiological signals. For demonstration purposes, we use GPIO (General Purpose Input- Output) to continuously poll for an event to occur. In general, the processor could be used in an interrupt mode, where an event generated by the FPAA fabric would be used to wake-up the processor.

R-R interval for ECG is calculated using a simple counter implemented on the processor in conjunction with the FPAA fabric. Assembly code is used to reduce the size of the SRAM cell needed to store the algorithm and in turn reduce the power consumption.

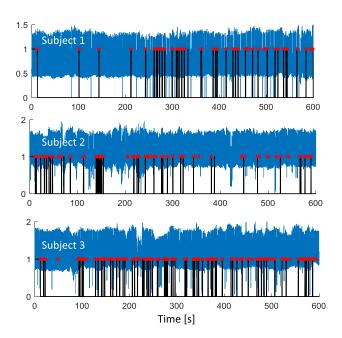

Fig. 11. Sinus arrhythmia detection on ECG data (blue) of three subjects from MIT-BIH database [27], [28]. The pulses (black) created by the cardiac processor timestamps the arrhythmia events annotated in the recordings (red dots).

TABLE I ARRHYTHMIA DETECTION PERFORMANCE

| Subject      | TP | FN | Se    |

|--------------|----|----|-------|

| P1 (Rec 114) | 33 | 0  | 100%  |

| P2 (Rec 210) | 49 | 3  | 94.2% |

| P3 (Rec 214) | 87 | 5  | 94.5% |

#### IV. CARDIAC PROCESSOR VALIDATION AND DISCUSSION

The FPAA R-wave detection algorithm simulations, which were performed using the models generated for the devices on the FPAA [33], resulted in an average sensitivity of Se = 94.2%for the 48 recordings in the MIT-BIH arrhythmia database. The cardiac processor outputs that timestamp abnormally long R-R sinus arrhythmia events are presented in Fig. 11. Red dots in Fig. 11 represent all beats with arrhythmia events such as premature ventricular contractions and rhythm changes in addition to degraded signal quality, as described in the Physionet Database. Over the course of ten minutes ECG datasets from three subjects true/false positive values and the positive predictive values for PVC and rhythm changes are summarized in Table I. A normal resting heart rate is 60 to 100 beats per minute (bpm). Arrhythmia events considered occur if HR reduces below 40 bpm or elevates to more than 140 bpm [41]. In these cases, the minimum deviations between two consecutive R-R intervals in an abnormal decrease and increase in HR can be 500 ms (HR: 60 bpm  $\rightarrow$  40 bpm) and 172 ms (HR: 100 bpm  $\rightarrow$  140 bpm), respectively. Our processor can detect minimum R-R interval variations greater than 50 ms. For each subject, we achieve detection sensitivity of at least 94.2%. Other low-power arrhythmia detection algorithms demonstrate detection sensitivities comparable to ours [42], [43]. It should be noted that, in our processor, a factor affecting the arrhythmia detection is the amplitudes of the R-waves. To illustrate, some of the arrhythmia events

TABLE II FEATURE DETECTION PERFORMANCE

| Subject | R-R Error      | SBP Error       | SpO <sub>2</sub> Error |

|---------|----------------|-----------------|------------------------|

| S1      | 29.9 ± 57.5 ms | -1.8 ± 2.5 mmHg | 5.1 ± 4.8 %            |

| S2      | 24.8 ± 22.7 ms | 1.24 ± 6.1 mmHg | 7.3 ± 7.7 %            |

| S3      | 24.1 ± 46.8 ms | -7.4 ± 6.4 mmHg | 5.6 ± 5.3 %            |

missed by our processor are short normal R-waves followed by tall abnormal R-waves. In that case, while the normal short R-wave is missed by the peak detector, the abnormal tall R-wave is tracked, which in some cases results in a normal R-R range. In future implementations, the arrhythmia detection can be made directly on pulses timestamping the detected R-waves, thereby potentially improving the arrhythmia detection sensitivity.

Additionally, SBP values obtained from the FPAA processor and a digital MATLAB algorithm, namely find peaks, finding the local maxima of the ABP waveforms in a given heart beat are compared. Lastly, SpO<sub>2</sub> calculations of the FPAA processor and digital calculations implemented on MATLAB are compared. These results are summarized in Table II. Percentage mean R-R errors for the subjects S1, S2, and S3 are 2.95%, 3.75% and 3.55%; respectively. Mean SBP calculation errors are 1.67% (S1), 1.06% (S2), and 6.27% (S3). SpO<sub>2</sub> variation over time is inherently prone to high-frequency noise due to the division operation involved. Therefore, the mean percentage SpO<sub>2</sub> errors in the Table II have been found after low-pass filtering both the analog (cardiac processor) and digital (MATLAB) SpO<sub>2</sub> outputs by a 4<sup>th</sup> order FIR filter ( $f_{-3dB} = 1 \,\mathrm{Hz}$ ). Despite the good correlation between the SpO<sub>2</sub> calculations of the analog circuitry and the DSP algorithms for the healthy subjects, there is a systematic error created by the dc offset of the  $V_{\rm mid}$  in Fig. 8. In future implementations, this offset can be removed by modifying the circuit to perform multiplication/division on current signals with zero offset [44]. Despite the good correlation between the SpO<sub>2</sub> calculations of the analog circuitry and the DSP algorithms for the healthy subjects, there is a systematic error created by the dc offset of the  $V_{\rm mid}$  in Fig. 8. In future implementations, this offset can be removed by modifying the circuit to perform multiplication/division on current signals with zero offset [44]; and thus, potentially reduce the SpO<sub>2</sub> errors to comply with the FDA guidance for pulse oximeters [45].

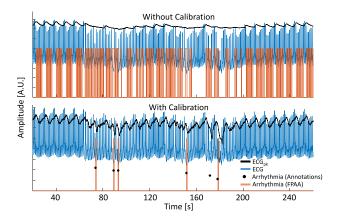

FG offers flexibility in terms of calibrating a mixed-signal system and mitigating the intrinsic mismatch present in a system. From the perspective of a system analyzing physiological and vital signs, this would enable healthcare workers to tailor/tune the system to meet the needs of a patient. Analog algorithm implementation on the FPAA enables controlling several parameters [34], [46]. Calibration is largely done in two ways. In the first type of calibration [46] the parameters are stored in a LUT format which can be used for subsequent programming of an FPAA. This calibration is for programming different FPAAs with the same high-level infrastructure. Parameters involve the bias voltages of the FG, time for tunneling and electron injection from or on to the floating node. Secondly, in a run time mode a BIST [34] system is used for tuning the circuits to certain specifications. For instance, we tune the offset of the FGOTA comparator, measured during runtime and followed

Fig. 12. The calibration of the cardiac processor is achieved through FG programming. In arrhythmia detection, a significant improvement is achieved with the calibration.

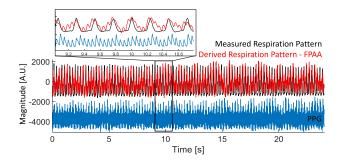

Fig. 13. Low-pass filtered peak detector output from a PPG signal can extract the respiration pattern.

by programming cycles, in Fig. 10 to obtain the results of the Fig. 12. The data recorded from different subjects will vary and hence it would necessitate subject specific calibration, similar to the performed for cochlear implants. Notably, the digital signal conditioning stage limits the signal amplitudes to 1  $V_{\rm pp}$ , and thus enabling subject-specific parameters to be calibrated for different subjects and recordings.

In this study, the focus has been given to three vital signs. However, the circuit architectures presented in this work can be used in monitoring other vital signs or cardiac features. For instance, the R-R monitoring approach can be expanded to monitor other periodic vital signs such as the respiration rate. Changes in intrathoracic pressure during inhalation and exhalation modulates the stroke volume and therefore amplitude of PPG signals, which reflects the changes in blood volume [47]. Therefore, to monitor the respiration rate, the peak value of one of the PPG signals can be LPF by a G<sub>m</sub>-C filter with a sub-Hz cutoff frequency to obtain the respiration pattern. The similarity between the extracted respiration pattern following that procedure and measured respiration pattern by a pneumatic respiration transducer are displayed in Fig. 13. For respiration rate calculation, the respiration waveform can be fed to a hysteretic differentiator followed by a comparator for generating pulses at the peaks.

The input dynamic range for the ECG, ABP, and PPG signals is  $\sim 1~V_{\rm pp}$ . For validation of the computation electronics, signal conditioning has been performed in the digital domain. However,

as an ultimate localized processor solution, signal conditioning may be achieved in the analog domain on the FPAA chip [48].

Table III shows the power consumption of analog components of the proposed system implemented on a reconfigurable and programmable analog platform. The Table III also shows the dynamic power consumption of the corresponding system implemented on a digital FPGA, fabricated on a 180 nm CMOS process and supplied by 3.3 V. The digital implementation computes with an 8-bit accuracy and clock frequency of 10 kHz. The power consumption is first-order estimate generated using PowerPlay Power Analysis tool provided by Intel for power estimation of Altera FPGAs. Additionally, the Table III shows the area utilization for an FPGA and the FPAA. The area for FPAA is noted in terms of CABs whereas for an FPGA it is noted in terms of logic elements. Logic elements of the FPGA, specifically the one used for comparison, consists of four-input Look-Up-Table (LUT) and a programmable register. It should also be noted that the FPAA consists of 98 CABs and the FPGA used here consists of 1270 logic elements.

To evaluate the performance, a comparison of the cardiac processor with the state-of-the-art real-time cardiac signal processing approaches is presented in Table IV. Cardiac processing in the state-of-the-art approaches are either purely in digital or mixed-signal domains. The processor presented can detect R-peaks with a sensitivity of 94.2% and arrhythmia with a sensitivity of 96.2% from ECG while outperforming the power performance of the most power-efficient digital ASIC alternative [50] by consuming  $\sim$ 87% less power. Two factors contribute to the power efficiency; (i) computing in the physical domain and (ii) facilitating the CMOS subthreshold region. Computing in the physical domain leads to simplicity. For instance, dc blocking, differentiation, and noise-suppression tasks are performed by a single hysteretic differentiator implemented using a FGOTA. To minimize the power consumption, majority of the devices are operated in subthreshold region by biasing via sub-nA currents.

Energy efficiency of the LED drive, sensing, and signal-conditioning electronics has been the focus of the efforts on design of wearable/implantable SpO<sub>2</sub> monitoring electronics. Among these studies, the ones computing perfusion index ratio in real-time commonly use microprocessors with current consumption values comparable to average current consumption of the LEDs, which is the highest power consumption block of a PPG sensing system [55]–[57]. One study in the literature demonstrates low-power real-time perfusion-index ratio computation [58]. Performing the computations in the analog domain, the signal processing circuitry in [58] consumes  $\sim$ 200  $\mu$ W, which is more than two orders of magnitude higher than the power consumption of the SpO<sub>2</sub> monitoring electronics of the cardiac processor presented.

Our approach of implementing the biosignal processing algorithms in the analog domain on an FPAA can be expanded to designing a custom analog-processor leveraging FG devices for programmability. Notably, the FG-programming in the FPAA processor is performed once to tune the parameters. Therefore, in a custom FG-based solution, the peripheral blocks needed for FG programming (e.g., ADC, DAC) can be designed to be detachable from the processor during the processing to minimize the footprint.

| System Block                      | FPAA Power<br>Consumption | FPAA Area<br>(Number of CABs)          | FPGA Power<br>Consumption | FPGA Area<br>(Number of Logic Elements) |

|-----------------------------------|---------------------------|----------------------------------------|---------------------------|-----------------------------------------|

| ECG R-R and arrhythmia detect     | 126 nW                    | 1 CAB (ECG R-R)<br>3 CABs (Arrhythmia) | 10 μW                     | 254 Logic Elements                      |

| SBP and DBP measurement circuitry | 251 nW                    | 1 CAB                                  | 3 μW                      | 48 Logic Elements                       |

| SpO <sub>2</sub> monitoring       | 1.44 μW                   | 5 CABs                                 | 50 μW                     | 672 Logic Elements                      |

| Cardiac Processor Total           | 1.82 μW                   | 10 CABs                                | 63 μW                     | 974 Logic Elements                      |

TABLE III

COMPARISON OF FPAA AND FPGA

TABLE IV PERFORMANCE COMPARISON

|              | Dragossing Domain                                            | Tuno / Toobnology           | Processing and Features/Accuracy <sup>a</sup> |                    |                             |

|--------------|--------------------------------------------------------------|-----------------------------|-----------------------------------------------|--------------------|-----------------------------|

|              | Processing Domain                                            | Type/ Technology            | R detect                                      | Arrhythmia detect  | Power Consumption           |

| This<br>Work | Analog                                                       | FPAA SoC/<br>350 nm         | Yes/<br>Se: 94.2% (R)<br>AE=3.4% (R-R)        | Yes/<br>Se: 96.2%  | 0.126 μW                    |

| [49]         | Analog (Feature Extraction)<br>Digital (Heartbeat detection) | ASIC/<br>180 nm + DSP chip  | Yes/<br>N/A                                   | No                 | 0.8 μW (Feature extraction) |

| [50]         | Digital                                                      | ASIC/<br>350 nm             | Yes/<br>+P:99.57% (R)                         | No                 | 0.96 μW                     |

| [51]         | Digital                                                      | ASIC/<br>65 nm              | Yes<br>N/A                                    | Yes/<br>PA: 86%    | 2.78 μW                     |

| [52]         | Digital                                                      | ASIC/<br>180 nm             | Yes/<br>+P:100% (R)                           | No                 | 43 μW                       |

| [53]         | Digital                                                      | ASIC /<br>180 nm + DSP chip | Yes/<br>N/A                                   | Yes/<br>DA: 97.25% | 459.967 μW                  |

| [54]         | Digital                                                      | ASIC/<br>65 nm              | Yes/<br>+P:99.49% (R)                         | No                 | 770 mW                      |

aSe: Average Sensitivity; AE: Average Error; +P = Positive Predictive Value; PA: Prediction Accuracy; Power consumption in [54] was calculated based on provided energy (0.11 mJ) and frequency (7 kHz) values.

#### V. CONCLUSION

This paper presents design and validation of an analog signal processor for energy-efficient vital sign monitoring at cardiac signal sensor node. The processor extracts important features from ECG, ABP, and PPG signals to detect the vital signs, compresses the cardiac signals in a physiologically-relevant manner, and generates warning signals in the events of sinus arrhythmia and low SpO<sub>2</sub> levels. The processor is implemented on an FPAA hardware embodying a programmable and reconfigurable FPAA chip and an on-chip microprocessor. The system performs the calculations in real-time. In addition, the analog R-R and SpO<sub>2</sub> outputs are logged to PC when an abnormality is detected, thus enabling further analysis offline. For energy efficiency, the circuitry has been designed in CMOS subthreshold region of operation. The system has been demonstrated using datasets from healthy subjects and patients and analog computation results match with offline processing outputs obtained by MATLAB algorithms. We envision the processing approach and circuit details detailed in this study laying the foundation for addressing the needs of the cardiac health sensor nodes of the future body sensor networks.

#### ACKNOWLEDGMENT

The authors would like to thank O. Inan and the members of the Inan Research Lab at Georgia Tech for assistance with data collection from healthy subjects and sharing the data.

#### REFERENCES

- [1] V. Higuera, "How is heart disease diagnosed?" May 2016. [Online]. Available: https://www.healthline.com/health/heart-disease/tests-diagnosis#modal-close, Accessed: Sept. 18, 2019.

- [2] Centers for Disease Control and Prevention, "Heart Failure Fact Sheet," Jun. 2016, [Online]. Available: https://www.cdc.gov/dhdsp/data\_ statistics/fact\_sheets/fs\_heart\_failure.htm, Accessed: Sept. 18, 2019.

- [3] A. Garg et al., "Clinical application of biomarkers in heart failure with a preserved ejection fraction: A review," Cardiology, vol. 136, no. 3, pp. 192–203, 2017.

- [4] A. R. Kemper et al., "Strategies for implementing screening for critical congenital heart disease," *Pediatrics*, vol. 128, no. 5, pp. e1259–e1267, 2011.

- [5] P. S. Hamilton and W. J. Tompkins, "Quantitative investigation of QRS detection rules using the MIT/BIH arrhythmia database," *IEEE Trans. Biomed. Eng.*, vol. 12, no. 12, pp. 1157–1165, Dec. 1986.

- [6] R. Mukkamala *et al.*, "Toward ubiquitous blood pressure monitoring via pulse transit time: Theory and practice," *IEEE Trans. Biomed. Eng.*, vol. 62, no. 8, pp. 1879–1901, Aug. 2015.

- [7] J. Allen, "Photoplethysmography and its application in clinical physiological measurement," *Physiol. Meas.*, vol. 28, no. 3, pp. R1–R39, 2007.

- [8] S. George et al., "A programmable and configurable mixed-mode FPAA SoC," *IEEE Trans. Very Large Scale Integration Syst.*, vol. 24, no. 6, pp. 2253–2261, Jun. 2016.

- [9] J. A. Walsh, E. J. Topol, and S. R. Steinhubl. "Novel wireless devices for cardiac monitoring," *Circulation*, vol. 130, no. 7, pp. 573–581, 2014.

- [10] Y.-T. Zhang and C. C. Y. Poon, "Health informatics: Unobtrusive physiological measurement technologies," *IEEE J. Biomed. Health Inform.*, vol. 17, no. 5, pp. 893–893, Sep. 2013.

- [11] H. J. Baek et al., "A smart health monitoring chair for nonintrusive measurement of biological signals," *IEEE Trans. Inf. Technol. Biomed.*, vol. 16, no. 1, pp. 150–158, Jan. 2012.

- [12] H. H. Asada et al., "Mobile monitoring with wearable photoplethysmographic biosensors," *IEEE Eng. Med. Biol. Mag.*, vol. 22, no. 3, pp. 28–40, May/Jun. 2003.

- [13] P. Celka et al., "Motion resistant earphone located infrared based heart rate measurement device," Biomed. Eng., 2004, doi: 10.2316/Journal.216.2004.2.417-033.

- [14] Z.-B. Zhang et al., "Design and implementation of sensing shirt for ambulatory cardiopulmonary monitoring," J. Med. Biol. Eng., vol. 31, no. 3, pp. 207–215, 2011.

- [15] A. Lanata, E. P. Scilingo, and D. D. Rossi, "A multimodal transducer for cardiopulmonary activity monitoring in emergency," *IEEE Trans. Inf. Technol. Biomed.*, vol. 14, no. 3, pp. 817–825, May 2010.

- [16] N. Suda et al., "A 65 nm programmable analog device array (panda) for analog circuit emulation," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 63, no. 2, pp. 181–190, Feb. 2016.

- [17] N. Guo et al., "Energy-efficient hybrid analog/digital approximate computation in continuous time," *IEEE J. Solid-State Circuits*, vol. 51, no. 7, pp. 1514–1524, Jul. 2016.

- [18] A. Basu et al., "Rasp 2.8: A new generation of floating-gate based field programmable analog array," in Proc. IEEE Custom Integrated Circuits Conf., Sep. 2008, pp. 213–216.

- [19] J. Hasler and H. B. Marr, "Finding a roadmap to achieve large neuromorphic hardware systems," *Frontiers Neurosci.*, vol. 7, pp. 118–146, 2013.

- [20] A. Basu et al., "A floating-gate-based field-programmable analog array," IEEE J. Solid-State Circuits, vol. 45, no. 9, pp. 1781–1794, Sep. 2010.

- [21] C. R. Schlottmann and P. E. Hasler, "A highly dense, low power, programmable analog vector-matrix multiplier: The fpaa implementation," *IEEE J. Emerg. Sel. Topics Circuits Syst.*, vol. 1, no. 3, pp. 403–411, Sep. 2011.

- [22] R. B. Wunderlich, F. Adil, and P. Hasler, "Floating gate-based field programmable mixed-signal array," *IEEE Trans. Very Large Scale Integration Syst.*, vol. 21, no. 8, pp. 1496–1505, Aug. 2013.

- [23] T. S. Hall et al., "Large-scale field-programmable analog arrays for analog signal processing," *IEEE Trans. Circuits Syst. I, Reg Papers*, vol. 52, no. 11, pp. 2298–2307, Nov. 2005.

- [24] C. D. Salthouse and R. Sarpeshkar, "A practical micropower programmable bandpass filter for use in bionic ears," *IEEE J. Solid-State Circuits*, vol. 38, no. 1, pp. 63–70, Jan. 2003.

- [25] E. K. F. Lee and P. G. Gulak, "A cmos field-programmable analog array," IEEE J. Solid-State Circuits, vol. 26, no. 12, pp. 1860–1867, Dec. 1991.

- [26] S. Kim, J. Hasler, and S. George, "Integrated floating-gate programming environment for system-level ICs," *IEEE Trans. Very Large Scale Integra*tion Syst., vol. 24, no. 6, pp. 2244–2252, Jun. 2016.

- [27] A. L. Goldberger et al., "Physiobank, physiotoolkit, and physionet: Components of a new research resource for complex physiologic signals," Circulation, vol. 101, no. 23, pp. e215–e220

- [28] A. E. W. Johnson et al., "MIMIC-III, a freely accessible critical care database," Sci. Data, vol. 3, 2016, Art. no. 160035.

- [29] M. Collins, J. Hasler, and S. George, "An open-source tool set enabling analog-digital-software co-design," *J. Low Power Electron. Appl.*, vol. 6, no. 1, pp. 3–14, 2016.

- [30] K. Yang and A. G. Andreou, "Multiple input floating-gate MOS differential amplifiers and applications for analog computation," in *Proc. 36th Midwest Symp. Circuits Syst.*, Aug. 1993, pp. 1212–1216.

- [31] R. Chawla et al., "Programmable G<sub>m</sub>—C filters using floating-gate operational transconductance amplifiers," IEEE Trans. Circuits Syst.—I, Reg. Papers, vol. 54, no. 3, pp. 481–491, Mar. 2007.

- [32] C. Mead, Analog VLSI and Neutral Systems. Reading, MA, USA: Addison-Wesley, 1989.

- [33] A. Natarajan and J. Hasler, "Modeling, simulation and implementation of circuit elements in an open-source tool set on the FPAA," *Analog Integr. Circuits Signal Process.*, vol. 91, pp. 119–130, 2017.

- [34] S. Shah and J. Hasler, "Tuning of multiple parameters with a BIST system," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 64, no. 7, pp. 1772–1780, Jul 2017

- [35] J. Pan and W. J. Tompkins, "A real-time QRS detection algorithm," *IEEE Trans. Biomed. Eng.*, vol. BME-32, no. 3, pp. 230–236, Mar. 1985.

- [36] M. Nitzan et al., "Pulse oximetry: Fundamentals and technology update," Med. Devices., vol. 7, pp. 231–239, Jul. 2014.

- [37] B. A. Minch, "Translinear analog signal processing: A modular approach to large-scale analog computation with multiple-input translinear elements," in *Proc. Adv. Res. VLSI*, Mar. 1999, pp. 186–199.

- [38] B. A. Minch et al., "Translinear circuits using subthreshold floating-gate MOS transistors," Analog Integr. Circuits Signal Process., vol. 9, pp. 167–179, Mar. 1996.

- [39] Centers for Disease Control and Prevention, "Atrial fibrillation fact sheet," Aug. 2017. [Online]. Available: https://www.cdc.gov/dhdsp/ data\_statistics/fact\_sheets/fs\_atrial\_fibrillation.htm, Accessed: Apr. 25, 2018

- [40] J. L. Fleg and H. L. Kennedy, "Cardiac arrhythmias in a healthy elderly population: Detection by 24-hour ambulatory electrocardiography," *Chest*, vol. 81, no. 3, pp. 302–307, 1982.

- [41] N. Sadr et al., "Reducing false arrhythmia alarms in the ICU by Hilbert QRS detection," in Proc. IEEE Comput. Cardiol. Conf., 2015, pp. 1173–1176.

- [42] S. Yin et al., "A 1.06-μW Smart ECG processor in 65-nm CMOS for real-time biometric authentication and personal cardiac monitoring," *IEEE J. Solid-State Circuits*, vol. 54, no. 8, pp. 2316–2326, Aug. 2019.

- [43] S.-Y. Hsu et al., "A 48.6-to-105.2 μW machine learning assisted cardiac sensor SoC for mobile healthcare applications," *IEEE J. Solid-State Cir*cuits, vol. 49, no. 4, pp. 801–811, Apr. 2014.

- [44] C. B. Güngör and H. Töreyin, "A 0.5 nW analog ECG processor for real time r-wave detection based on pan-tompkins algorithm," presented at IEEE BHI, 2019.

- [45] U. S. Food and D. Administration, "Pulse oximeters—Premarket notification submissions [510 k(k) s]: Guidance for industry and food and drug administration staff," US Department of Health and Human Services, Washington, DC, USA, 2013.

- [46] S. Kim, S. Shah, and J. Hasler, "Calibration of floating-gate SoC FPAA system," *IEEE Trans. Very Large Scale Integration Syst.*, vol. 25, no. 9, pp. 2649–2657, Sep. 2017.

- [47] P. H. Charlton *et al.*, "Breathing rate estimation from the electrocardiogram and photoplethysmogram: A review," *IEEE Rev. Biomed. Eng.*, vol. 11, pp. 2–20, 2017.

- [48] A. Zbrzeski et al., "A programmable bioamplifier on FPAA for in vivo neural recording," in Proc. IEEE Biomed. Circuits Syst. Conf., Nov. 2010, pp. 114–117.

- [49] L. Yan et al., "A 13 μA analog signal processing IC for accurate recognition of multiple intra-cardiac signals," *IEEE Trans. Biomed. Circuits Syst.*, vol. 7, no. 6, pp. 785–795, Dec. 2013.

- [50] C. J. Deepu et al., "A 3-lead ECG-on-chip with QRS detection and lossless compression for wireless sensors," *IEEE Trans. Cir*cuits Syst. II, Express Briefs, vol. 63, no. 12, pp. 1151–1155, Dec. 2016.

- [51] N. Bayasi et al., "Low-power ecg-based processor for predicting ventricular arrhythmia," *IEEE Trans. Very Large Scale Integration Syst.*, vol. 24, no. 5, pp. 1962–1974, Oct. 2015.

- [52] H. Kim et al., "A configurable and low-power mixed signal SoC for portable ECG monitoring applications," *IEEE Trans. Biomed. Circuits Syst.*, vol. 8, no. 2, pp. 257–267, Apr. 2014.

- [53] S.-Y. Lee *et al.*, "Low-power wireless ECG acquisition and classification system for body sensor networks," *IEEE J. Biomed. Health Inform.*, vol. 19, no. 1, pp. 236–246, Jan. 2015.

- [54] Y. Zou et al., "An energy-efficient design for ECG recording and R-peak detection based on wavelet transform," *IEEE Trans. Circuits Syst. II, Express Briefs*, vol. 62, no. 2, pp. 119–123, 2015

- [55] L. Sant et al., "A 13.2b optical proximity sensor system with 130 klx ambient light rejection capable of heart rate and blood oximetry monitoring," *IEEE J. Solid-State Circuits*, vol. 51, no. 7, pp. 1674–1683, Jul. 2016.

- [56] M. Konijnenburg et al., "A multi (bio) sensor acquisition system with integrated processor, power management, 8 × 8 LED drivers, and simultaneously synchronized ECG, BIO-Z, GSR, and two PPG readouts," *IEEE J. Solid State Circuits*, vol. 51, no. 11, pp. 2584–2595, Nov. 2016.

- [57] P. Schönle et al., "Towards an implantable telemetry system for SpO<sub>2</sub> and PWV measurement in small animals," in Proc. IEEE Biomed. Circuits Syst. Conf., Oct. 2017, pp. 596–599.

- [58] M. Tavakoli, L. Turicchia, and R. Sarpeshkar, "An ultra-low-power pulse oximeter implemented with an energy-efficient transimpedance amplifier," *IEEE Trans. Biomed. Circuits Syst.*, vol. 4, no. 1, pp. 27–38, Feb. 2010.

- [59] B. Rumberg et al., "Hibernets: Energy-efficient sensor networks using analog signal processing," *IEEE J. Emerg. Sel. Topics Circuits Syst.*, vol. 1, no. 3, pp. 321–334, Sep. 2011.