Page 9.0-1

#### Outline

- Section 9.1 Switched Capacitor Circuits

- Section 9.2 Switched Capacitor Amplifiers

- Section 9.3 Switched Capacitor Integrators

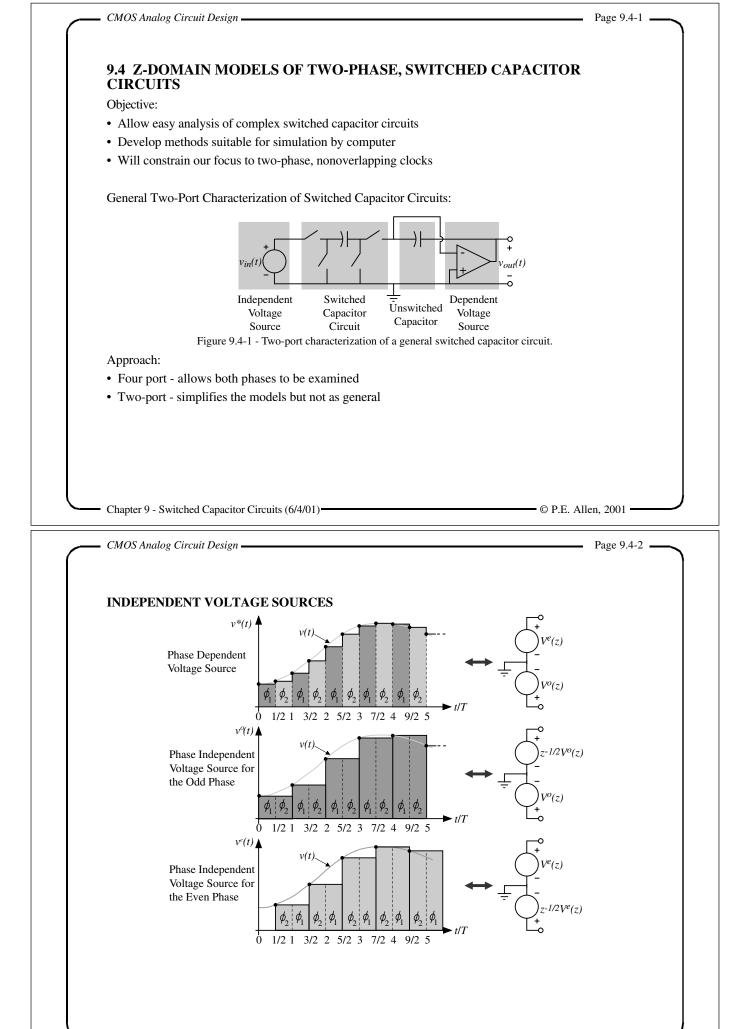

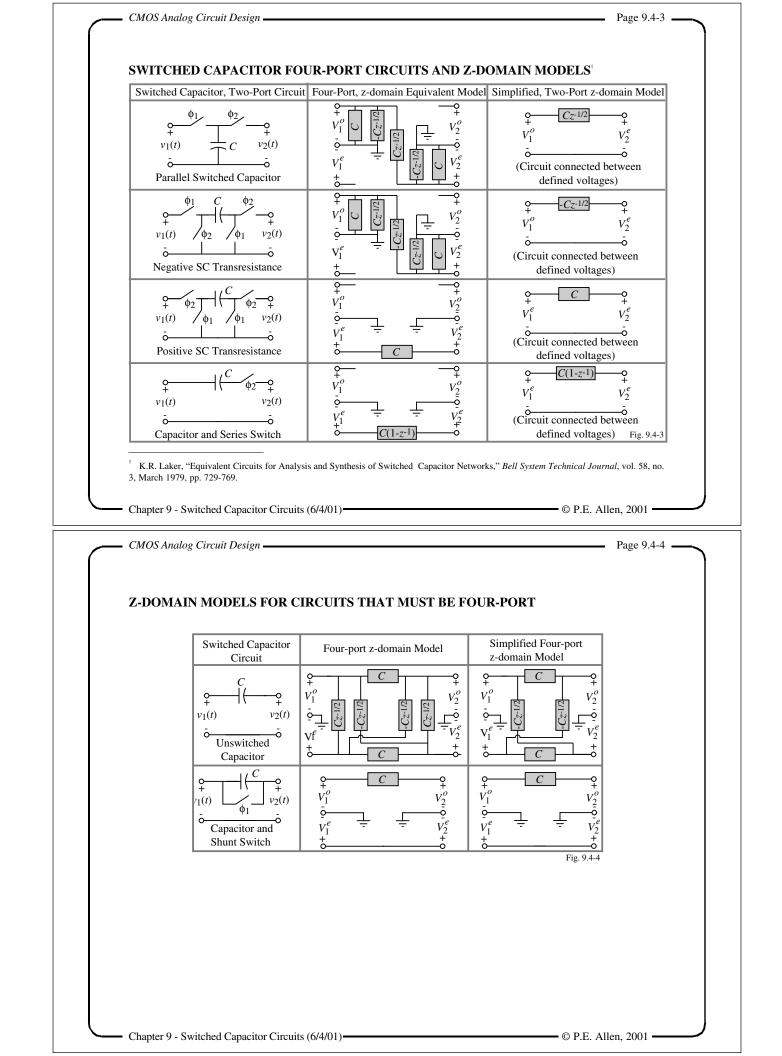

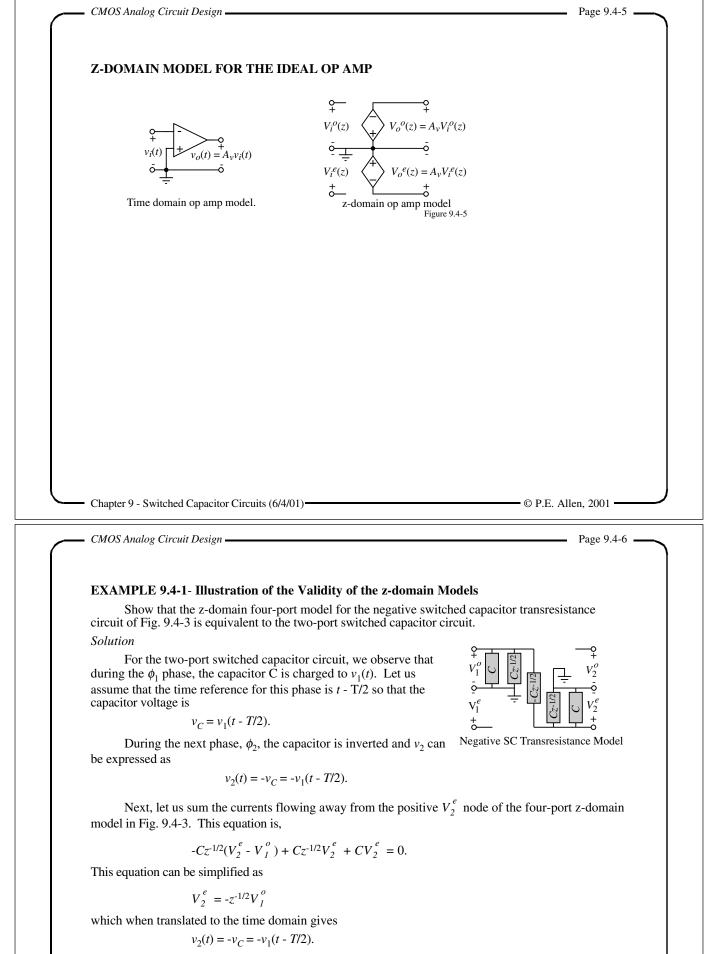

Section 9.4 - z-domain Models of Two-Phase, Switched Capacitor Circuits, Simulation

Section 9.5 - First-order, Switched Capacitor Circuits

Section 9.6 - Second-order, Switched Capacitor Circuits

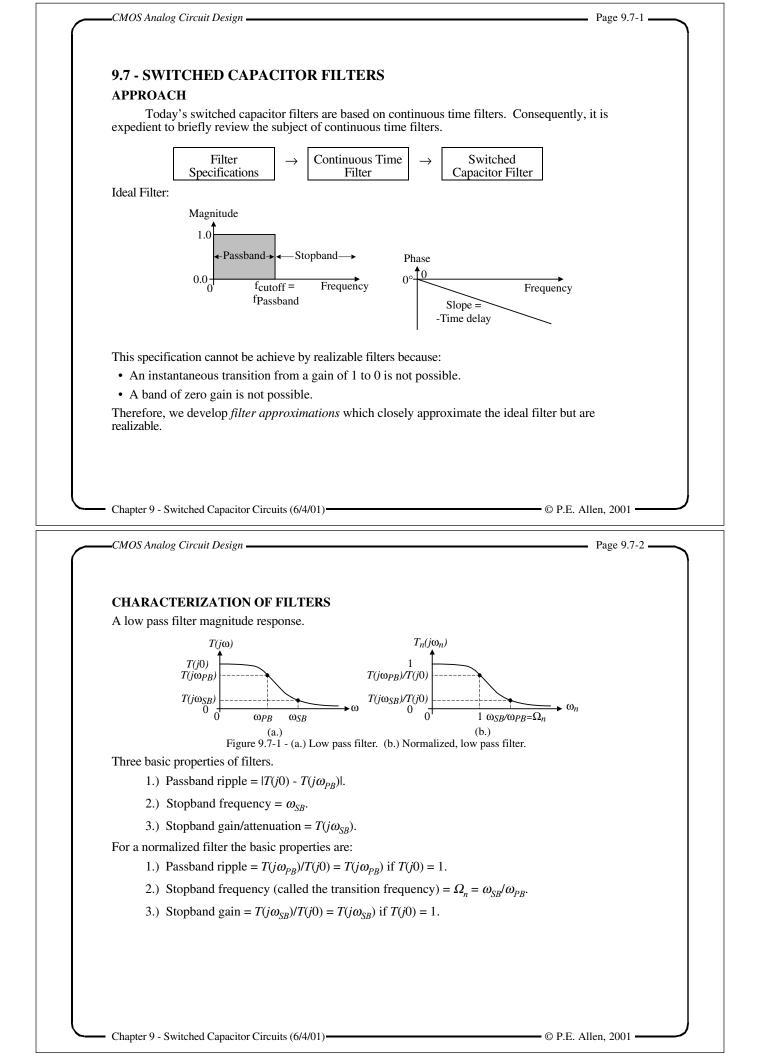

Section 9.7 - Switched Capacitor Filters

Section 9.8 - Summary

Chapter 9 - Switched Capacitor Circuits (6/4/01)-

- © P.E. Allen, 2001

Page 9.1-1

Analog CMOS Circuit Deisgn -

# 9.1 - SWITCHED CAPACITOR CIRCUITS

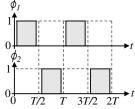

## **RESISTOR EMULATION**

Switched capacitor circuits are not new. James Clerk Maxwell used switches and a capacitor to measure the equivalent resistance of a galvanometer in the 1860's.

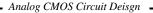

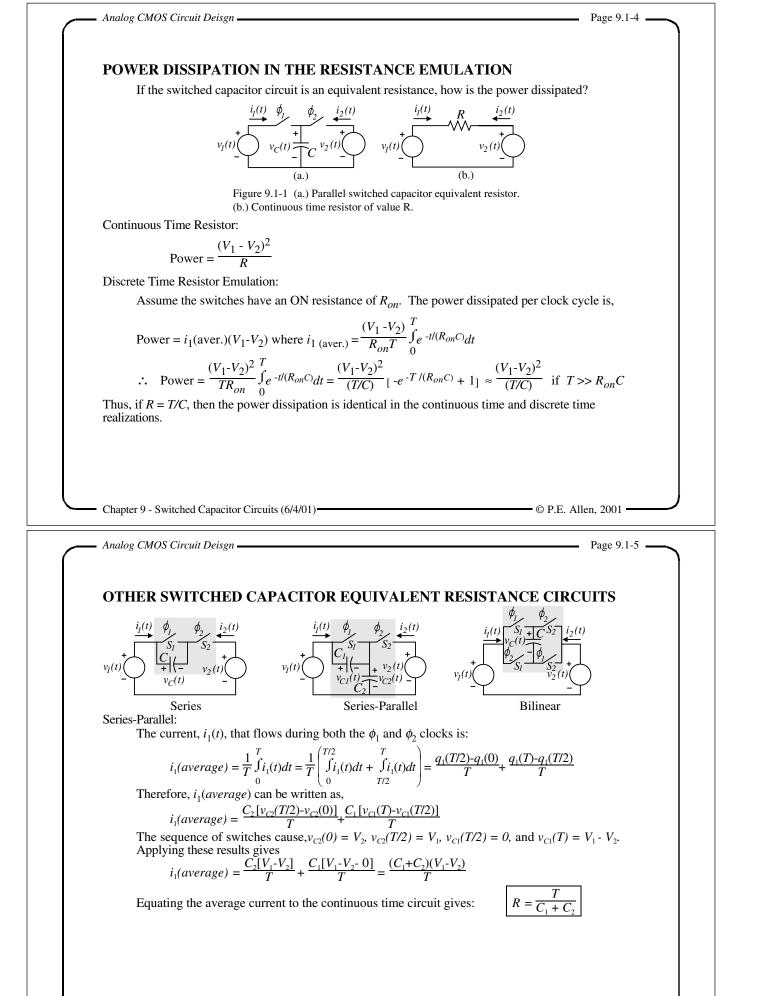

Parallel Switched Capacitor Equivalent Resistor:

Figure 9.1-1 (a.) Parallel switched capacitor equivalent resistor. (b.) Continuous time resistor of value R.

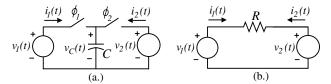

Two-Phase, Nonoverlapping Clock:

Figure 9.1-2 - Waveforms of a typical two-phase, nonoverlapping clock scheme.

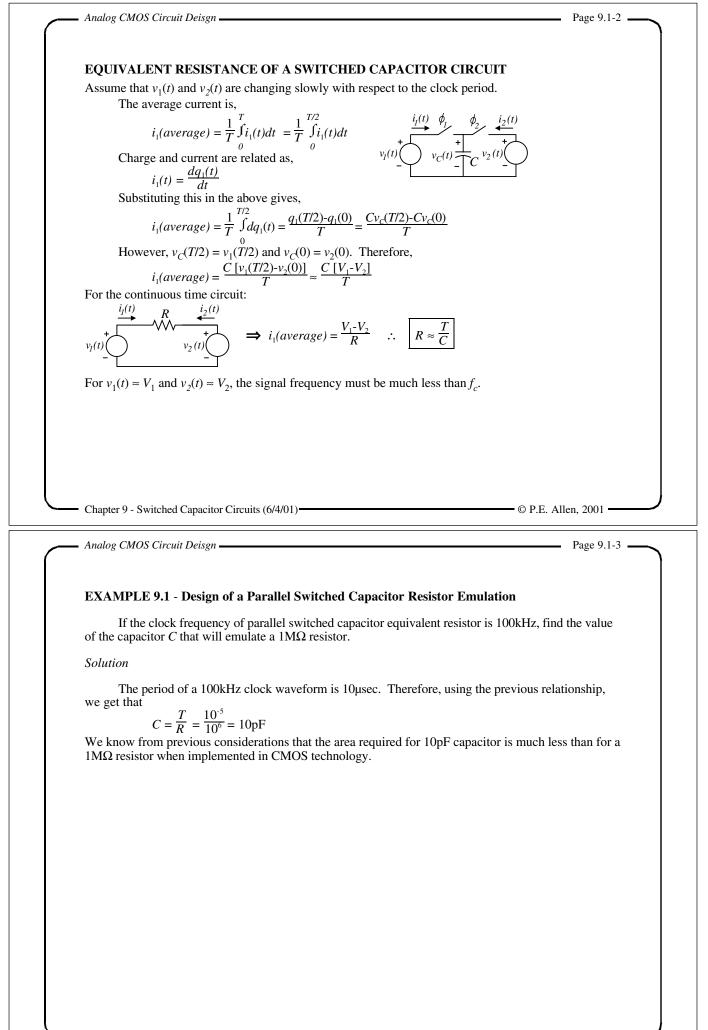

# EXAMPLE 9.1-2 - Design of a Series-Parallel Switched Capacitor Resistor Emulation

If C1 = C2 = C, find the value of C that will emulate a 1M $\Omega$  resistor if the clock frequency is 250kHz.

Solution

The period of the clock waveform is 4µsec. Using above relationship we find that C is given as,  $2C = \frac{T}{R} = \frac{4x10^{-6}}{10^6} = 4\text{pF}$

Therefore, C1 = C2 = C = 2pF.

Chapter 9 - Switched Capacitor Circuits (6/4/01)

© P.E. Allen, 2001

Page 9.1-7

Analog CMOS Circuit Deisgn -

# SUMMARY OF THE FOUR SWITCHED CAPACITOR RESISTANCE CIRCUITS

| Switched Capacitor<br>Resistor Emulation Circuit | Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Equivalent Resistance                 |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Parallel                                         | $\begin{array}{c} \phi_1 \\ \phi_2 \\ \psi_1(t) \\ \overline{o} \\ \end{array} \\ \hline \end{array} \\ \begin{array}{c} \phi_2 \\ \psi_2(t) \\ \overline{o} \\ \overline{o} \\ \end{array} \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\frac{T}{C}$                         |

| Series                                           | $ \begin{array}{c}                                     $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\frac{T}{C}$                         |

| Series-Parallel                                  | $ \begin{array}{c}                                     $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\frac{T}{C_1^{\circ} + ^{\circ}C_2}$ |

| Bilinear                                         | $ \begin{array}{c}  \phi_1 & \phi_2 \\  \phi_2 & \phi_1 & \phi_2 \\  \phi_1 & \phi_2 & \phi_2 & \phi_2 & \phi_2 & \phi_2 \\  \phi_1 & \phi_2 & \phi_2 & \phi_2 & \phi_2 \\  \phi_2 & \phi_1 & \phi_2 & \phi_2 & \phi_2 & \phi_2 & \phi_2 & \phi_2 \\  \phi_1 & \phi_2 & \phi_2 & \phi_2 & \phi_2 & \phi_2 & \phi_$ | $\frac{T}{4C}$                        |

#### Page 9.1-8

Consider the following continuous time, first-order, low pass circuit:

The transfer function of this simple circuit is,

$$H(j\omega) = \frac{V_2(j\omega)}{V_1(j\omega)} = \frac{1}{j\omega R_1 C_2 + 1} = \frac{1}{j\omega \tau_1 + 1}$$

where  $\tau_1 = R_1 C_2$  is the time constant of the circuit and determines the accuracy.

Continuous Time Accuracy

Let  $\tau_1 = \tau_C$ . The accuracy of  $\tau_C$  can be expressed as,

$\frac{d\tau_c}{\tau_c} = \frac{dR_1}{R_1} + \frac{dC_2}{C_2} \implies 5\% \text{ to } 20\% \text{ depending on the size of the components}$ Discrete Time Accuracy Let  $\tau_1 = \tau_D = \left(\frac{\tilde{T}}{C_1}\right)C_2 = \left(\frac{1}{f_*C_1}\right)C_2$ . The accuracy of  $\tau_D$  can be expressed as,

$\frac{d\tau_D}{\tau_D} = \frac{dC_2}{C_2} - \frac{dC_1}{C_1} - \frac{df_c}{f_c} \implies 0.1\% \text{ to } 1\% \text{ depending on the size of components}$

The above is the primary reason for the success of switched capacitor circuits in CMOS technology.

Chapter 9 - Switched Capacitor Circuits (6/4/01)-

- © P.E. Allen, 2001

Analog CMOS Circuit Deisgn -

#### Page 9.1-10

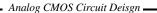

# ANALYSIS METHODS FOR TWO-PHASE, NONOVERLAPPING CLOCKS - CONT'D

Time-domain Relationships:

The previous figure showed that,

$$v^*(t) = v^o(t) + v^e(t)$$

$(\phi_2).$

where the superscript *o* denotes the odd phase  $(\phi_1)$  and the superscript *e* denotes the even phase  $\phi_1$ .

For any given sample point, t = nT/2, the above may be expressed as

$$v^* \left(\frac{nT}{2}\right)_{n=1,2,3,4,5,6,\cdots} = v^{o} \left(\frac{nT}{2}\right)_{n=1,3,5,\cdots} + v^{e} \left(\frac{nT}{2}\right)_{n=2,4,5,\cdots}$$

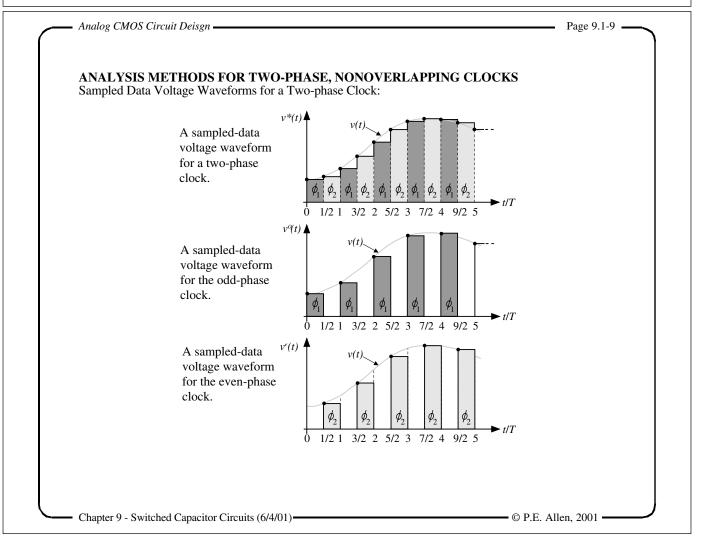

z-domain Relationships:

Consider the one-sided z-transform of a sequence, v(nT), defined as

$$V(z) = \sum_{n=0}^{\infty} v(nT)z^{-n} = v(0) + v(T)z^{-1} + v(2T)z^{-2} + \cdots$$

for all z for which the series V(z) converges.

Now, this equation can be expressed in the z-domain as

$V^*(z) = V^0(z) + V^e(z) \,.$

The z-domain format for switched capacitor circuits will allow us to analyze transfer functions.

Chapter 9 - Switched Capacitor Circuits (6/4/01)

© P.E. Allen, 2001

Page 9.1-11

Analog CMOS Circuit Deisgn -

## TRANSFER FUNCTION VIEWPOINT OF SWITCHED CAPACITOR CIRCUITS

Input-output voltages of a general switched capacitor circuit in the z-domain.

$$V_i(z) = V_i^{o}(z) + V_i^{o}(z) \longrightarrow V_o(z) = V_o^{o}(z) + V_o^{o}(z)$$

Switched

Capacitor

Circuit

$\phi_1^{\uparrow} \phi_2^{\uparrow}$

z-domain transfer functions:

$$H^{ij}(z) = \frac{V_o^j(z)}{V_i^i(z)}$$

where *i* and *j* can be either *e* or *o*. For example,  $H^{oe}(z)$  represents  $V_o^e(z)/V_i^o(z)$ . Also, a transfer function, H(z) can be defined as

$$H(z) = \frac{V_o(z)}{V_i(z)} = \frac{V_o^e(z) + V_o^o(z)}{V_i^e(z) + V_i^o(z)} \ .$$

| APPROACH FOR ANALYZING SWITCHED CAPACITOR CIRCUITS         1.) Analyze the circuit in the time-domain during a selected phase period.         2.) The resulting equations are based on $q = Cv$ .         3.) Analyze the following phase period carrying over the initial conditions from the previous analysis         4.) Identify the time-domain equation that relates the desired voltage variables.         5.) Convert this equation to the z-domain.         6.) Solve for the desired z-domain transfer function.         7.) Replace z by $e^{j\omega T}$ and examine the frequency response.         Chapter 9 - Switched Capacitor Circuits (6/4/01)         © Chapter 9 - Switched Capacitor Circuits (6/4/01)         @ P.E. Allen, 2001         Analog CMOS Circuit Deisgn         Page 9.1         EXAMPLE 9.1-3 - Analysis of a Switched Capacitor, First-order, Low pass Filter         Use the above approach to find the z-domain transfer function of the first-order, low pass |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <ul> <li>2.) The resulting equations are based on <i>q</i> = <i>Cv</i>.</li> <li>3.) Analyze the following phase period carrying over the initial conditions from the previous analysis</li> <li>4.) Identify the time-domain equation that relates the desired voltage variables.</li> <li>5.) Convert this equation to the <i>z</i>-domain.</li> <li>6.) Solve for the desired <i>z</i>-domain transfer function.</li> <li>7.) Replace <i>z</i> by <i>e<sup>iaT</sup></i> and examine the frequency response.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| <ul> <li>Analog CMOS Circuit Deisgn Page 9.1</li> <li>EXAMPLE 9.1-3 - Analysis of a Switched Capacitor, First-order, Low pass Filter Use the above approach to find the z-domain transfer function of the first-order, low pass</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | s.   |

| Analog CMOS Circuit Deisgn     Page 9.1     EXAMPLE 9.1-3 - Analysis of a Switched Capacitor, First-order, Low pass Filter     Use the above approach to find the z-domain transfer function of the first-order, low pass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| <ul> <li>Analog CMOS Circuit Deisgn Page 9.1</li> <li>EXAMPLE 9.1-3 - Analysis of a Switched Capacitor, First-order, Low pass Filter Use the above approach to find the z-domain transfer function of the first-order, low pass</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| Analog CMOS Circuit Deisgn Page 9.1 <b>EXAMPLE 9.1-3 - Analysis of a Switched Capacitor, First-order, Low pass Filter</b> Use the above approach to find the z-domain transfer function of the first-order, low pass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| <ul> <li>Analog CMOS Circuit Deisgn Page 9.1</li> <li>EXAMPLE 9.1-3 - Analysis of a Switched Capacitor, First-order, Low pass Filter Use the above approach to find the z-domain transfer function of the first-order, low pass</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| <b>EXAMPLE 9.1-3 - Analysis of a Switched Capacitor, First-order, Low pass Filter</b><br>Use the above approach to find the z-domain transfer function of the first-order, low pass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1    |

| <b>EXAMPLE 9.1-3 - Analysis of a Switched Capacitor, First-order, Low pass Filter</b><br>Use the above approach to find the z-domain transfer function of the first-order, low pass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1-13 |

| switched capacitor circuit shown below. This circuit was developed by replacing the resistor, $R_1$ , of t<br>previous circuit with the parallel switched capacitor resistor circuit. The timing of the clocks is also<br>shown. This timing is arbitrary and is used to assist the analysis and does not change the result.<br>$ \begin{array}{c}                                     $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | the  |

| Solution<br>$\phi_{\underline{1}}: (n-1)T \le t \le (n-0.5)T$<br>Equivalent circuit:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| $v_{1}^{o}(n-1)T C_{1}  C_{2} \xrightarrow{+} v_{2}^{e}(n-\frac{3}{2})T v_{2}^{o}(n-1)T \qquad v_{1}^{o}(n-1)T C_{1} \xrightarrow{+} v_{2}^{e}(n-\frac{3}{2})T v_{2}^{o}(n-1)T$ Equivalent circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| The voltage at the output (across $C_2$ ) is $v_2^o(n-1)T = v_2^e(n-3/2)T$ (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

(3)

#### **EXAMPLE 9.1-3 - Continued**

$$v_{1}^{e}(n-1/2)T \bigcirc_{-}^{C_{1}} v_{1}^{o}(n-1)T \bigcirc_{-}^{C_{2}} v_{2}^{o}(n-1)T} v_{2}^{o}(n-1)T \bigcirc_{-}^{C_{2}} v_{2}^{o}(n-1)T} v_{2}^{o}(n-1)T \bigcirc_{-}^{C_{2}} v_{2}^{o}(n-1)T O_{-}^{C_{2}} v_{2}^{o}(n-1)T O_{-}^{C_{2}$$

The output of this circuit can be expressed as the superposition of two voltage sources,

$$v_1^o(n-1)T$$

and  $v_2^o(n-1)T$  given as

$v_2^e(n-1/2)T = \left(\frac{C_1}{C_1+C_2}\right)v_1^o(n-1)T + \left(\frac{C_2}{C_1+C_2}\right)v_2^o(n-1)T.$  (2)

If we advance Eq. (1) by one full period, T, it can be rewritten as

$$v_2^o(n)T = v_2^e(n-1/2)T.$$

Substituting, Eq. (3) into Eq. (2) yields the desired result given as

$$v_2^{o}(nT) = \left(\frac{C_1}{C_1 + C_2}\right) v_1^{o}(n-1)T + \left(\frac{C_2}{C_1 + C_2}\right) v_2^{o}(n-1)T.$$

(4)

Chapter 9 - Switched Capacitor Circuits (6/4/01)

Page 9.1-15

#### Analog CMOS Circuit Deisgn -

# EXAMPLE 9.1-3 - Continued

z-domain Analysis

The next step is to write the z-domain equivalent expression for Eq. (4). This can be done term by term using the sequence shifting property given as

$$v(n - n_1)T \leftrightarrow z^{-n_1}V(z) .$$

<sup>(5)</sup>

The result is

$$V_2^o(z) = \left(\frac{C_1}{C_1 + C_2}\right) z^{-1} V_1^o(z) + \left(\frac{C_2}{C_1 + C_2}\right) z^{-1} V_2^o(z).$$

(6)

Finally, solving for  $V_2^o(z)/V_1^o(z)$  gives the desired z-domain transfer function for the switched capacitor circuit of this example as

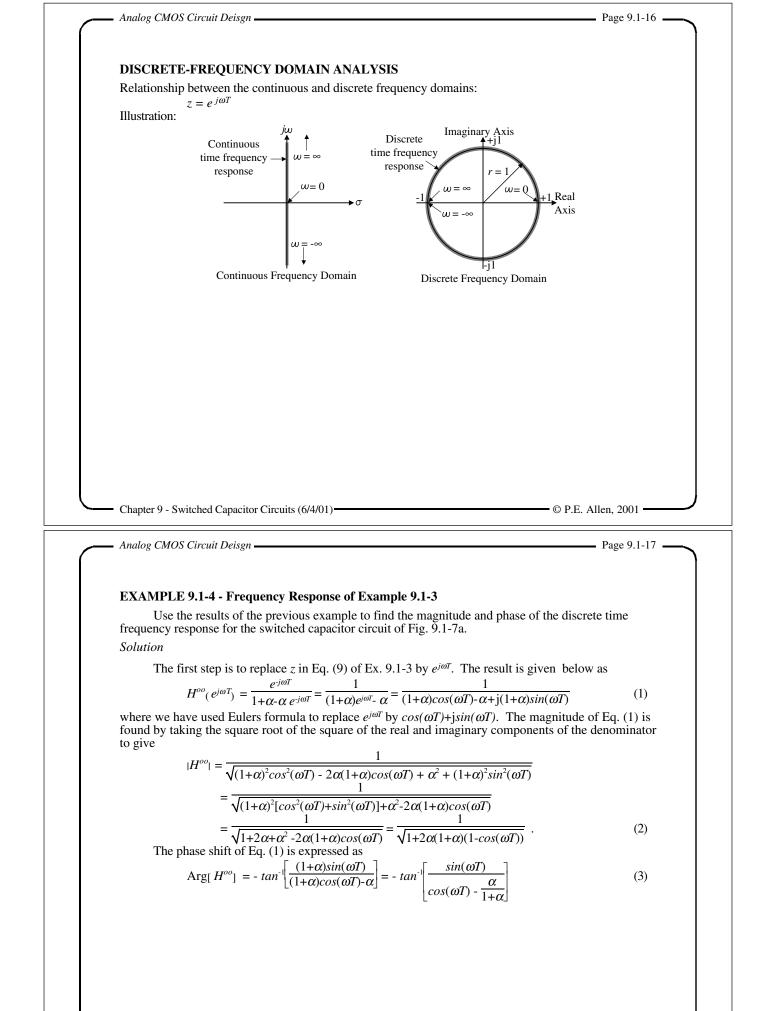

$$H^{oo}(z) = \frac{V_2^o(z)}{V_1^o(z)} = \frac{z^{-1}\left(\frac{C_1}{C_1 + C_2}\right)}{1 - z^{-1}\left(\frac{C_2}{C_1 + C_2}\right)} = \frac{z^{-1}}{1 + \alpha - \alpha z^{-1}} \text{, where } \alpha = \frac{C_2}{C_1}.$$

(7)

#### THE OVERSAMPLING ASSUMPTION

The oversampling assumption is simply to assume that  $f_{signal} \ll f_{clock} = f_c$ .

This means that,

$$f_{signal} = f << \frac{l}{T} \Rightarrow 2\pi f = \omega << \frac{2\pi}{T} \Rightarrow \omega T << 2\pi.$$

The importance of the oversampling assumption is that is permits the design of switched capacitor circuits that approximates the continuous time circuit until the signal frequency begins to approach the clock frequency.

Chapter 9 - Switched Capacitor Circuits (6/4/01)-

Page 9.1-19

- © P.E. Allen, 2001

#### Analog CMOS Circuit Deisgn -

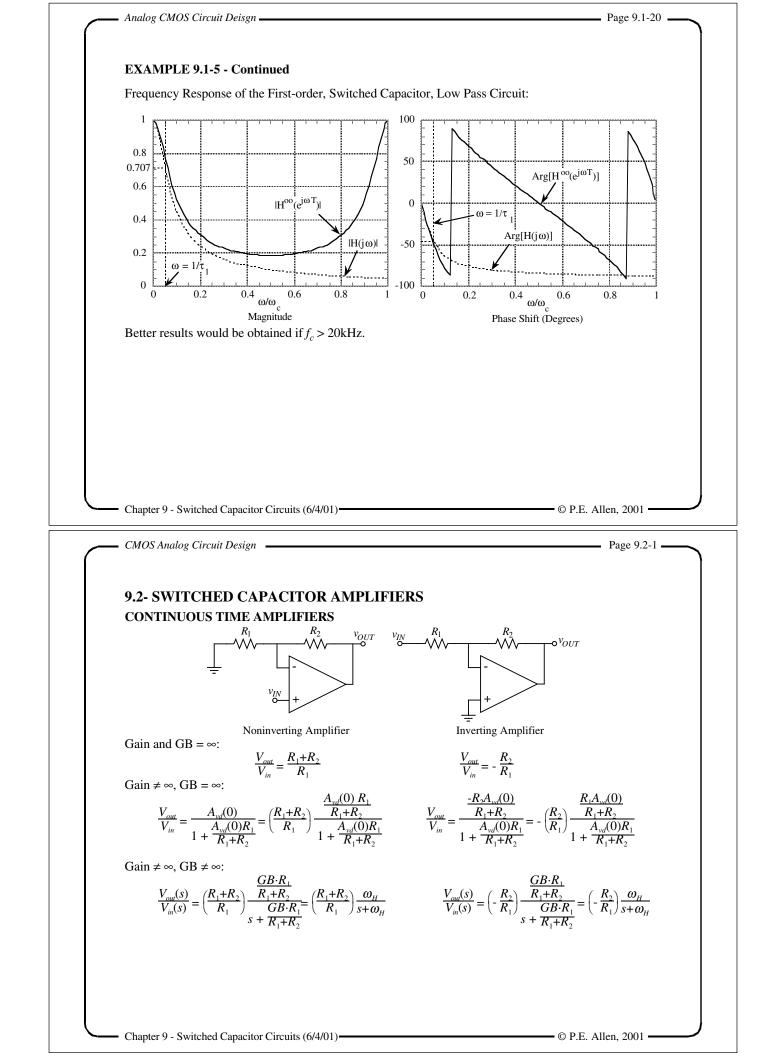

# EXAMPLE 9.1-5 - Design of Switched Capacitor Circuit and Resulting Frequency Response

Design the first-order, low pass, switched capacitor circuit of Ex. 9.1-3 to have a -3dB frequency at 1kHz. Assume that the clock frequency is 20kHz Plot the frequency response for the resulting discrete time circuit and compare with a first-order, low pass, continuous time filter. *Solution*

If we assume that  $\omega T$  is less than unity, then  $cos(\omega T)$  approaches 1 and  $sin(\omega T)$  approaches  $\omega T$ . Substituting these approximations into the magnitude response of Eq. (2) of Ex. 9.1-4 results in

$$\mathbf{H}^{oo}(e^{j\omega T}) \approx \frac{1}{(1+\alpha) \cdot \alpha + \mathbf{j}(1+\alpha)\omega T} = \frac{1}{1 + \mathbf{j}(1+\alpha)\omega T}.$$

(1)

Comparing this equation to the simple, first-order, low pass continuous time circuit results in the following relationship which permits the design of the circuit parameter  $\alpha$ .

$$\omega \tau_1 = (1 + \alpha) \omega T \tag{2}$$

Solving for  $\alpha$  gives

$$\alpha = \frac{\tau_1}{T} - 1 = f_c \tau_1 - 1 = \frac{f_c}{\omega_{.3dB}} - 1 = \frac{\omega_c}{2\pi\omega_{.3dB}} - 1 .$$

(3)

Using the values given, we see that  $\alpha = (20/6.28) \cdot 1 = 2.1831$ . Therefore,  $C_2 = 2.1831C_1$ .

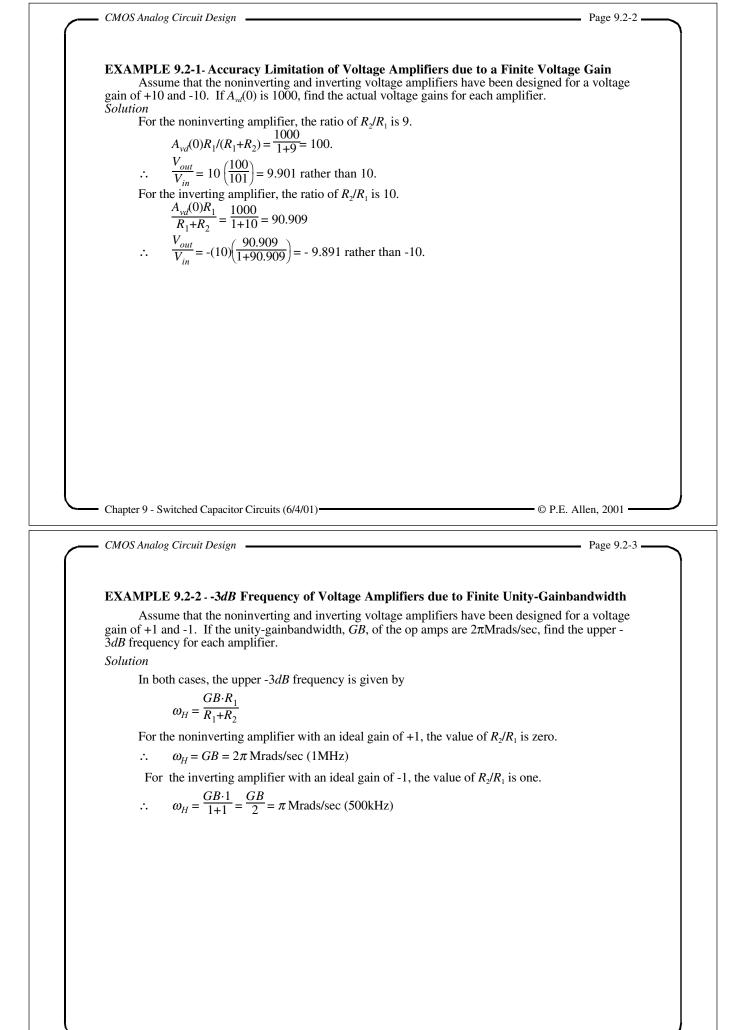

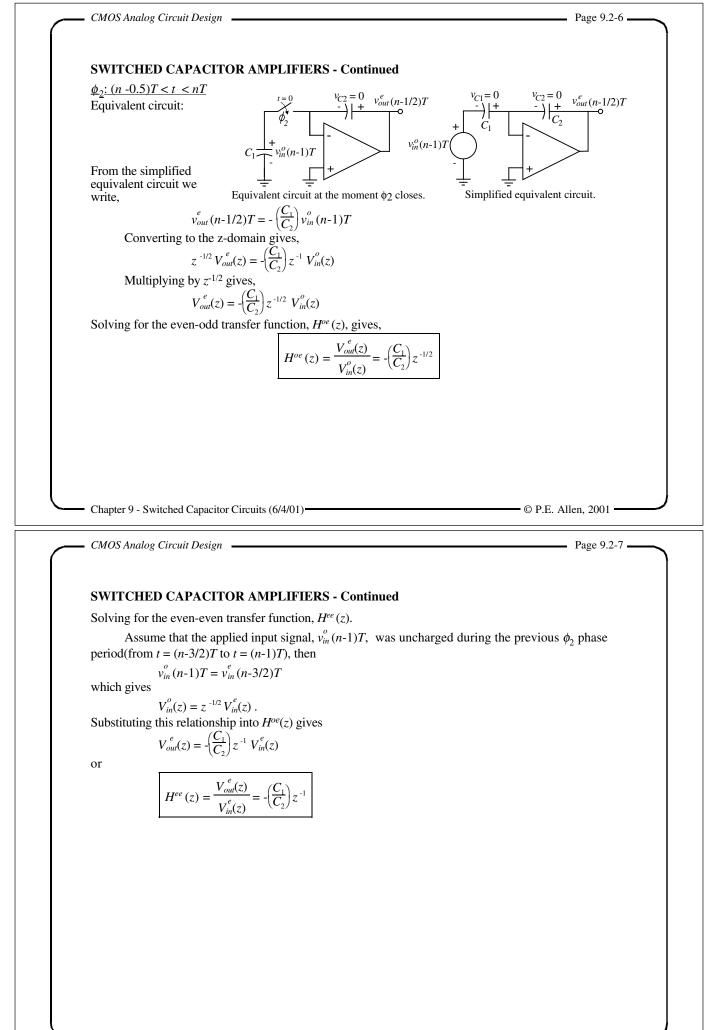

#### Page 9.2-8

## FREQUENCY RESPONSE OF SWITCHED CAPACITOR AMPLIFIERS

Replace z by  $e^{j\omega T}$ .

$$H^{oe}(e^{j\omega T}) = \frac{V_{out}^{e}(e^{j\omega T})}{V_{in}^{o}(e^{j\omega T})} = -\left(\frac{C_1}{C_2}\right)e^{-j\omega T/2}$$

and

$$H^{ee}\left(e^{j\omega T}\right) = \frac{V_{out}^{e}\left(e^{j\omega T}\right)}{V_{in}^{e}\left(e^{j\omega T}\right)} = -\left(\frac{C_{1}}{C_{2}}\right)e^{-j\omega T}$$

If  $C_1/C_2$  is equal to  $R_2/R_1$ , then the magnitude response is identical to inverting unity gain amplifier. However, the phase shift of  $H^{oe}(e^{j\omega T})$  is

$\operatorname{Arg}[H^{oe}(e^{j\omega T})] = \pm 180^{\circ} - \omega T/2$

and the phase shift of  $H^{oe}(e^{j\omega T})$  is

$\operatorname{Arg}[H^{ee}(e^{j\omega T})] = \pm 180^{\circ} - \omega T.$

Comments:

- The phase shift of the switched capacitor inverting amplifier has an excess linear phase delay.

- When the frequency is equal to  $0.5f_c$ , this delay is 90°.

- One must be careful when using switched capacitor circuits in a feedback loop because of the excess phase delay.

Chapter 9 - Switched Capacitor Circuits (6/4/01)

- © P.E. Allen, 2001

Page 9.2-9

CMOS Analog Circuit Design

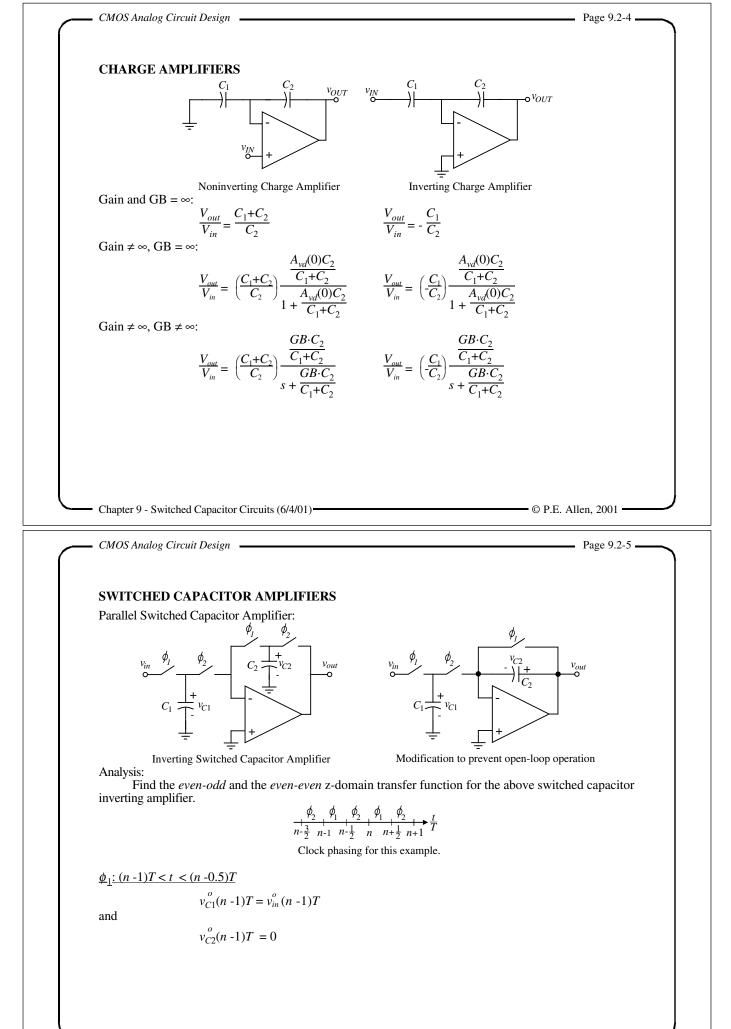

#### POSITIVE AND NEGATIVE TRANSRESISTANCE EQUIVALENT CIRCUITS

Transresistance circuits are two-port networks where the voltage across one port controls the current flowing between the ports. Typically, one of the ports is at zero potential (virtual ground). Circuits:

Positive Transresistance Realization.

Analysis (Negative transresistance realization):

$$R_T = \frac{v_1(t)}{i_2(t)} = \frac{v_1}{i_2(average)}$$

Negative Transresistance Realization.

If we assume  $v_1(t)$  is approximately constant over one period of the clock, then we can write

$$i_2(average) = \frac{1}{T} \int_{T/2}^{T} i_2(t)dt = \frac{q_2(T) - q_2(T/2)}{T} = \frac{Cv_C(T) - Cv_C(T/2)}{T} = \frac{-Cv_1}{T}$$

Substituting this expression into the one above shows that

$$R_T = -T/C$$

Similarly, it can be shown that the positive transresistance is T/C.

Comments:

• These results are only valid when  $f_c >> f$ .

• These circuits are insensitive to the parasitic capacitances shown as dotted capacitors.

CMOS Analog Circuit Design

Page 9.2-10

vout

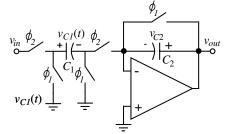

#### NONINVERTING STRAY INSENSITIVE SWITCHED CAPACITOR AMPLIFIER

$\xrightarrow{\phi_2 \ \phi_1 \ \phi_2 \ \phi_1 \ \phi_2 \ \phi_1 \ \phi_2}_{n-\frac{3}{2} \ n-1 \ n-\frac{1}{2} \ n \ n+\frac{1}{2} \ n+1} \phi_1 \phi_2$

Clock phasing for this example

Analysis:

$\phi_1: (n-1)T < t < (n-0.5)T$

The voltages across each capacitor can be written as

$$v_{C1}^{o}(n-1)T = v_{in}^{o}(n-1)T$$

and

$$v_{C2}^{o}(n-1)T = v_{out}^{o}(n-1)T = 0$$

$\frac{\phi_2: (n - 0.5)T < t < nT}{\text{The voltage across } C_2 \text{ is}}$

$$v_{out}^{e}(n-1/2)T = \left(\frac{C_1}{C_2}\right) v_{in}^{o}(n-1)T$$

Noninverting Switched Capacitor Voltage Amplifier.

$$V_{out}^{e}(z) = \left(\frac{C_1}{C_2}\right) z^{-1/2} V_{in}^{o}(z) \rightarrow H^{*oe}(z) = \left(\frac{C_1}{C_2}\right) z^{-1/2}$$

If the applied input signal,  $v_{in}^{o}(n-1)T$ , was unchanged during the previous  $\phi_2$  phase period above becomes

$$V_{out}^{e}(z) = \left(\frac{C_1}{C_2}\right) z^{-1} V_{in}^{e}(z) \quad \rightarrow \quad H^{\circ ee}(z) = \left(\frac{C_1}{C_2}\right) z^{-1}$$

Comments:

• Excess phase of  $H^{oe}(e^{j\omega T})$  is  $-\omega T/2$  and for  $H^{ee}(e^{j\omega T})$  is  $-\omega T$

Chapter 9 - Switched Capacitor Circuits (6/4/01)-

- © P.E. Allen, 2001

Page 9.2-11

CMOS Analog Circuit Design

# INVERTING STRAY INSENSITIVE SWITCHED CAPACITOR AMPLIFIER

Analysis:

# $\phi_1: (n-1)T < t < (n-0.5)T$

The voltages across each capacitor can be written as

$v_{C1}^{o}(n-1)T = 0$

and

$$v_{C2}^{o}(n-1)T = v_{out}^{o}(n-1)T = 0$$

$\underline{\phi}_{\underline{2}}: (n - 0.5)T < t < nT$

The voltage across  $C_2$  is

$$v_{out}^{e}(n-1/2)T = -\left(\frac{C_1}{C_2}\right)v_{in}^{e}(n-1/2)T$$

$$V_{out}^{e}(z) = -\left(\frac{C_1}{C_2}\right)V_{in}^{o}(z) \rightarrow H^{\circ oe}(z)$$

Inverting Switched Capacitor Voltage Amplifier.

• The inverting switched capacitor amplifier has no excess phase delay.

$\frac{C_1}{C_2}$

• There is no transfer of charge during  $\phi_1$ .

CMOS Analog Circuit Design

#### Page 9.2-12

- © P.E. Allen, 2001 -

CMOS Analog Circuit Design

# NONINVERTING SWITCHED CAPACITOR INTEGRATOR - Continued

#### $\underline{\phi}_1 : nT < t < (n + 0.5)T$

If we advance one more phase period, i.e. t = (n)T to t = (n-1/2)T, we see that the voltage at the output is unchanged. Thus, we may write

$$v_{out}^{o}(n)T = v_{out}^{e}(n-1/2)T.$$

Substituting this relationship into the previous gives the desired time relationship expressed as

$$v_{out}^{o}(n)T = \left(\frac{C_1}{C_2}\right)v_{in}^{o}(n-1)T + v_{out}^{o}(n-1)T$$

Transferring this equation to the z-domain gives,

$$V_{out}^{o}(z) = \left(\frac{C_1}{C_2}\right) z^{-1} V_{in}^{o}(z) + z^{-1} V_{out}^{o}(z) \rightarrow H^{oo}(z) = \frac{V_{out}^{o}(z)}{V_{in}^{o}(z)} = \left(\frac{C_1}{C_2}\right) \frac{z^{-1}}{1 - z^{-1}} = \left(\frac{C_1}{C_2}\right) \frac{1}{z - 1}$$

Replacing z by  $e^{j\omega T}$  gives,

$$H^{oo}(e^{j\omega T}) = \frac{V_{out}^{o}(e^{j\omega T})}{V_{in}^{o}(e^{j\omega T})} = \left(\frac{C_{1}}{C_{2}}\right) \frac{1}{e^{j\omega T} - 1} = \left(\frac{C_{1}}{C_{2}}\right) \frac{e^{-j\omega T/2}}{e^{j\omega T/2} - e^{-j\omega T/2}}$$

Replacing  $e^{j\omega T^2} - e^{-j\omega T^2}$  by its equivalent trigonometric identity, the above becomes

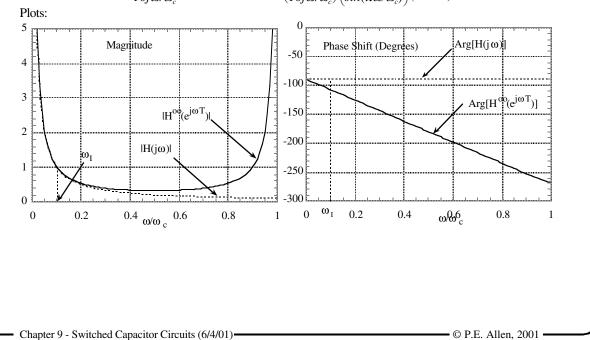

$$H^{oo}(e^{j\omega T}) = \frac{V_{out}^{o}(e^{j\omega T})}{V_{in}^{o}(e^{j\omega T})} = \left(\frac{C_1}{C_2}\right) \frac{e^{j\omega T/2}}{j2 \sin(\omega T/2)} \left(\frac{\omega T}{\omega T}\right) = \left(\frac{C_1}{j\omega T C_2}\right) \left(\frac{\omega T/2}{\sin(\omega T/2)}\right) (e^{-j\omega T/2})$$

$H^{oo}(e^{j\omega T}) = (\text{Ideal}) \times (\text{Magnitude error}) \times (\text{Phase error}) \text{ where } \omega_l = \frac{C_1}{TC_2} \Rightarrow \text{ Ideal} = \frac{\omega_l}{j\omega}$

Chapter 9 - Switched Capacitor Circuits (6/4/01)-

- © P.E. Allen, 2001

Page 9.3-6

#### CMOS Analog Circuit Design

# EXAMPLE 9.3-2 - Comparison of a Continuous Time and Switched Capacitor Integrator

Assume that  $\omega_l$  is equal to  $0.1\omega_c$  and plot the magnitude and phase response of the noninverting continuous time and switched capacitor integrator from 0 to  $\omega_l$ .

Solution

Page 9.3-5

#### **FINITE OP AMP GAIN - Continued**

Substitute the z-domain variable, z, with  $e^{jwT}$  to get

$$H^{oo}(e^{j\omega T}) = \frac{H_{f}(e^{j\omega T})}{1 - \frac{1}{A_{vd}(0)} \left[1 + \frac{C_{1}}{2C_{2}}\right] - j \frac{C_{1}/C_{2}}{2A_{vd}(0) \tan\left(\frac{\omega T}{2}\right)}$$

where now  $H_i(e^{j\omega T})$  is the integrator transfer function for  $A_{ud}(0) = \infty$ .

The error of an integrator can be expressed as

$$H(j\omega) = \frac{H_{l}(j\omega)}{[1-m(\omega)] e^{-j\theta(\omega)}}$$

where

$m(\omega)$  = the magnitude error due to  $A_{vd}(0)$

$\theta(\omega)$  = the phase error due to  $A_{vd}(0)$

TT ( · ...)

If  $\theta(\omega)$  is much less than unity, then this expression can be approximated by

$$H(j\omega) \approx \frac{H_{\Lambda}(j\omega)}{1 - m(\omega) - j\theta(\omega)}$$

(2)

Comparing Eq. (1) with Eq. (2) gives the magnitude and phase error due to a finite value of  $A_{vvl}(0)$  as

$$m(j\omega) = -\frac{1}{A_{vd}(0)} \left[ 1 + \frac{C_1}{2C_2} \right] \qquad \text{and} \qquad \theta(j\omega) = \frac{C_1/C_2}{2A_{vd}(0) \tan\left(\frac{\omega T}{2}\right)}$$

Chapter 9 - Switched Capacitor Circuits (6/4/01)-

© P.E. Allen, 2001

#### - Page 9.3-12 -

Page 9.3-11

(1)

#### EXAMPLE 9.3-3 - Evaluation of the Integrator Errors due to a finite value of $A_{vd}(0)$

Assume that the clock frequency and integrator frequency of a switch capacitor integrator is 100kHz and 10kHz, respectively. If the value of  $A_{vd}(0)$  is 100, find the value of  $m(j\omega)$  and  $\theta(j\omega)$  at 10kHz.

Solution

The ratio of  $C_1$  to  $C_2$  is found as

$$\frac{C_1}{C_2} = \omega_t T = \frac{2\pi \cdot 10,000}{100,000} = 0.6283$$

Substituting this value along with that for  $A_{vd}(0)$  into  $m(j\omega)$  and  $\theta(j\omega)$  gives

$$m(j\omega) = -\left[1 + \frac{0.6283}{2}\right] = -0.0131$$

and

$$\theta(j\omega) = \frac{0.6283}{2 \cdot 100 \cdot \tan(18^\circ)} = 0.554^\circ$$

The "ideal" switched capacitor transfer function,  $H_i(j\omega)$ , will be multiplied by a value of approximately 1/1.0131 = 0.987 and will have an additional phase lag of approximately  $0.554^{\circ}$ .

In general, the phase shift error is more serious than the magnitude error.

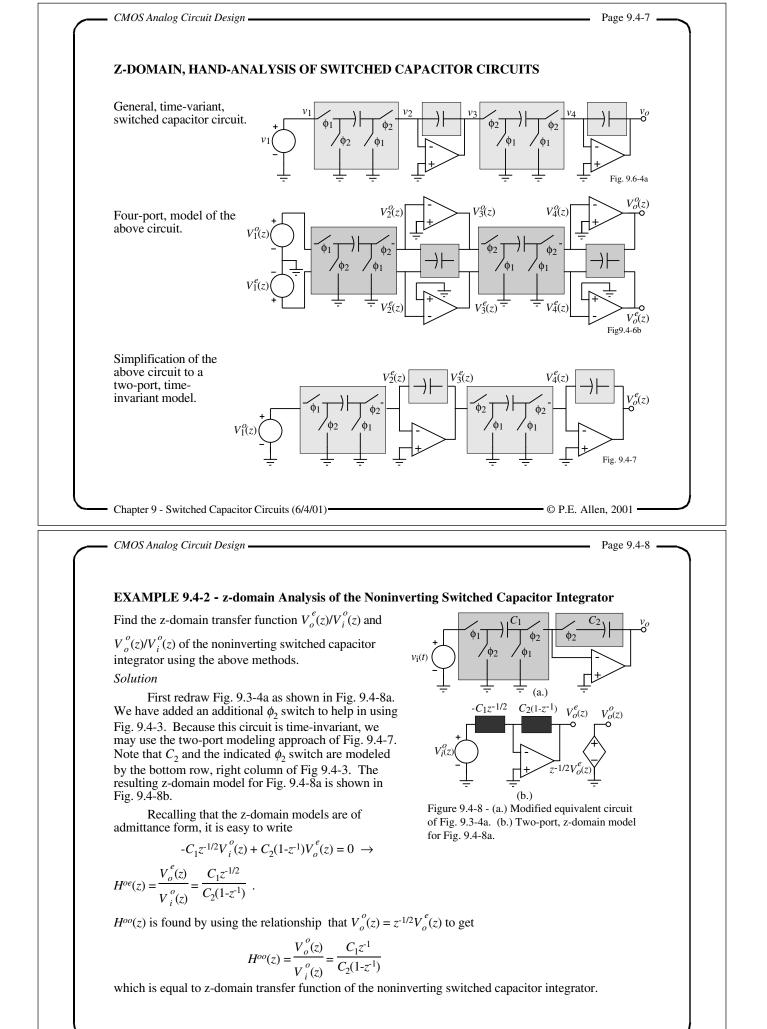

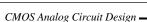

Thus, we have shown that the four-port z-domain model is equivalent to the time domain circuit for the above consideration.

$C_{2}$

$V_o^e(z) = V_o^o(z)$

- © P.E. Allen, 2001

Page 9.4-10

(a.)  $C_2(1-z^{-1})$

(b.) Figure 9.4-9 - (a.) Modified equivalent circuit of inverting SC integrator. (b.) Two-port, z-domain

$C_1$

model for Fig. 9.4-9a

#### EXAMPLE 9.4-3 - z-domain Analysis of the Inverting Switched Capacitor Integrator

Find the z-domain transfer function  $V_{a}^{e}(z)/V_{i}^{e}(z)$

and  $V_{0}^{o}(z)/V_{i}^{e}(z)$  of Fig. 9.3-4a using the above methods. Solution

Fig. 9.4-9a shows the modified equivalent circuit of Fig. 9.3-4b. The two-port, z-domain model for Fig. 9.4-9a is shown in Fig. 9.4-9b. Summing the currents flowing to the inverting node of the op amp gives

$$C_1 V_i^e(z) + C_2(1-z^{-1}) V_o^e(z) = 0$$

which can be rearranged to give

$$H^{ee}(z) = \frac{V_o^e(z)}{V_o^e(z)} = \frac{-C_1}{C_2(1-z^{-1})} .$$

which is equal to inverting, switched capacitor integrator z-domain transfer function.

$H^{eo}(z)$  is found by using the relationship that  $V_a^o(z) = z^{-1/2} V_a^e(z)$  to get

$$H^{eo}(z) = \frac{V_o^{b}(z)}{V_i^{e}(z)} = \frac{C_1 z^{-1/2}}{C_2 (1 - z^{-1})}.$$

Chapter 9 - Switched Capacitor Circuits (6/4/01)-

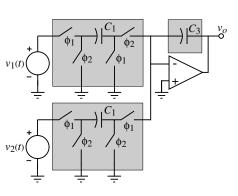

# EXAMPLE 9.4-4 - z-domain Analysis a Time-Variant Switched Capacitor Circuit

Find  $V_{a}^{o}(z)$  and  $V_{a}^{e}(z)$  as function of  $V_{1}^{o}(z)$  and

$V_2^{o}(z)$  for the summing, switched capacitor integrator of Fig. 9.4-10a.

#### Solution

This circuit is time-variant because  $C_3$  is charged from a different circuit for each phase. Therefore, we must use a four-port model. The resulting z-domain model for Fig. 9.4-10a is shown in Fig. 9.4-10b.

Fig. 9.4-10a - Summing Integrator.

#### **EXAMPLE 9.4-4 - Continued**

Summing the currents flowing away from the  $V_i^o(z)$  node gives

$$C_2 V_2^o(z) + C_3 V_o^o(z) - C_3 z^{-1/2} V_o^e(z) = 0$$

(1)

Summing the currents flowing away from the  $V_i^e(z)$  nodes gives

$$C_1 z^{-1/2} V_1^o(z) - C_3 z^{-1/2} V_o^o(z) + C_3 V_o^e(z) = 0$$

(2)

Multiplying (2) by  $z^{-1/2}$  and adding it to (1) gives

$$C_2 V_2^o(z) + C_3 V_o^o(z) - C_1 z^{-1} V_1^o(z) - C_3 z^{-1} V_o^o(z) = 0$$

(3)

Solving for  $V_o^o(z)$  gives,

$$V_o^o(z) = \frac{C_1 z^{-1} V_1^o(z)}{C_3(1-z^{-1})} - \frac{C_2 V_2^o(z)}{C_3(1-z^{-1})}$$

Multiplying Eq. (1) by  $z^{-1/2}$  and adding it to Eq. (2) gives

$$C_2 z^{-1/2} V_2^o(z) - C_1 z^{-1} V_1^o(z) - C_3 z^{-1} V_o^e(z) + C_3 V_o^e(z) = 0$$

Solving for  $V_o^e(z)$  gives,

$$V_o^e(z) = \frac{C_1 z^{-1/2} V_1^o(z)}{C_3(1 - z^{-1})} - \frac{C_2 z^{-1/2} V_2^o(z)}{C_3(1 - z^{-1})} \ .$$

Chapter 9 - Switched Capacitor Circuits (6/4/01)-

CMOS Analog Circuit Design -

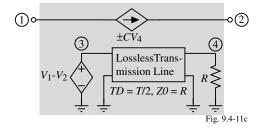

# FREQUENCY DOMAIN SIMULATION OF SWITCHED CAPACITOR CIRCUITS USING SPICE

#### **Storistors**<sup>†</sup>

A storistor is a two-terminal element that has a current flow that occurs at some time after the voltage is applied across the storistor.

z-domain:

$$I(z) = \pm C z^{-1/2} \left[ V_1(z) - V_2(z) \right]$$

Time-domain:

$$i(t) = \pm C \left[ v_1 \left( t - \frac{T}{2} \right) - v_2 \left( t - \frac{T}{2} \right) \right]$$

**SPICE** Primitives:

Page 9.4-11

$V_o^o(z)$

$-C_{3z}-1/2$

$-C_{3Z}-1/2$

Fig. 9.4-10b - Four-port, z-domain

- © P.E. Allen, 2001

Page 9.4-12

model for Fig. 9.4-10a.

$C_{1Z}$ -1/2

<sup>†</sup> B.D. Nelin, "Analysis of Switched-Capacitor Networks Using General-Purpose Circuit Simulation Programs," *IEEE Trans. on Circuits and Systems*, pp. 43-48, vol. CAS-30, No. 1, Jan. 1983.

CMOS Analog Circuit Design -

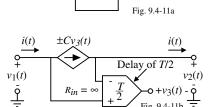

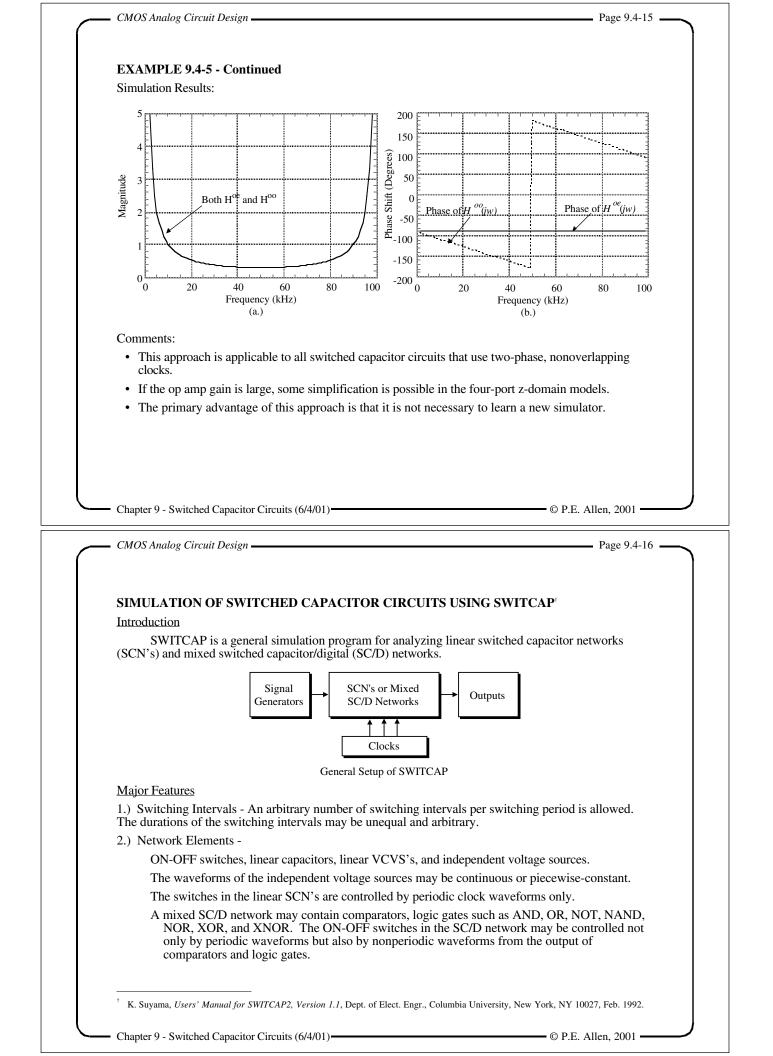

#### EXAMPLE 9.4-5 - SPICE Simulation of Example 9.4-2

Use SPICE to obtain a frequency domain simulation of the noninverting, switched capacitor integrator. Assume that the clock frequency is 100kHz and design the ratio of  $C_1$  and  $C_2$  to give an integration frequency of 10kHz.

<u>Solution</u>

The design of  $C_1/C_2$  is accomplished from the ideal integrator transfer function.

$$\frac{C_1}{C_2} = \omega_I T = \frac{2\pi f_I}{f_c} = 0.6283$$

Assume  $C_2 = 1F \rightarrow C_1 = 0.6283F$ .

Next we replace the switched capacitor  $C_1$  and the unswitched capacitor of integrator by the z-domain model of the second row of Fig. 9.4-3 and the first row of Fig. 9.4-4 to obtain Fig. 9.4-12. Note that in addition we used Fig. 9.4-5 for the op amp and assumed that the op amp had a differential voltage gain of 10<sup>6</sup>. Also, the unswitched *C*'s are conductances.

Figure 9.4-12 - z-domain model for noninverting switched capacitor integrator.

As the op amp gain becomes large, the important components are indicated by the darker shading.

Chapter 9 - Switched Capacitor Circuits (6/4/01)-

- © P.E. Allen, 2001 ·

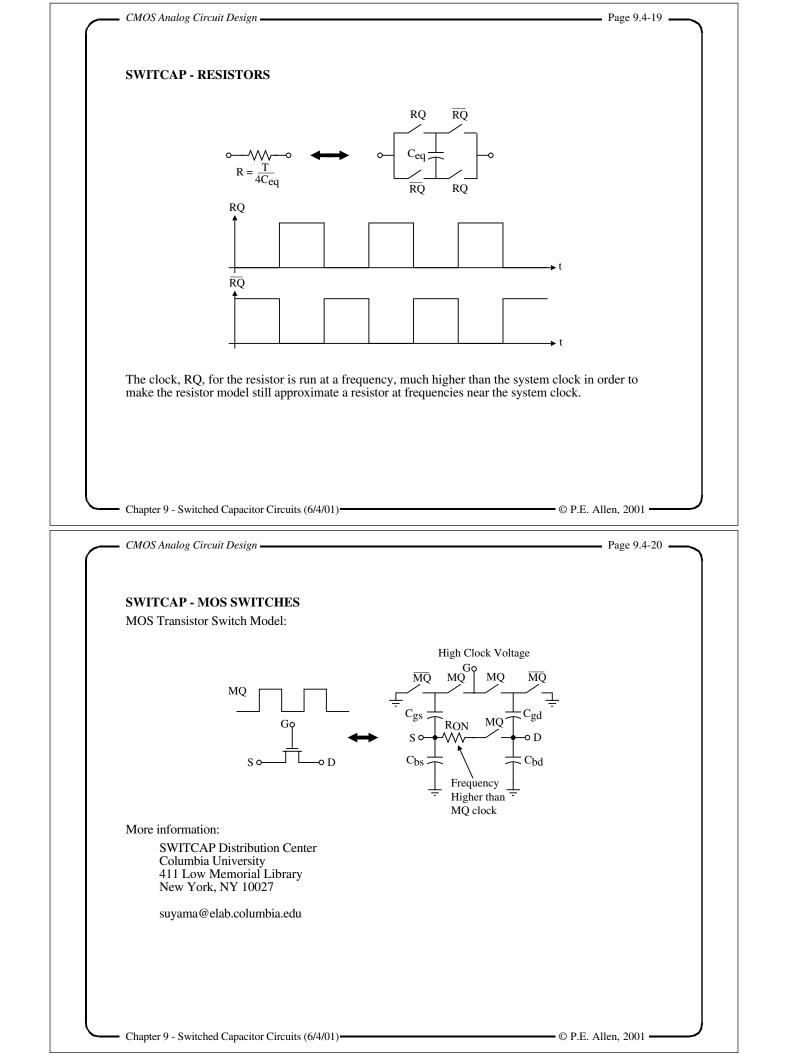

#### SWITCAP - Major Features, Continued

3.) Time-Domain Analyses of Linear SCN's and Mixed SC/D Networks -

- a.) Linear SCN's only: The transient response to any prescribed input waveform for  $t \ge 0$  after computing the steady-state values for a set of dc inputs for t < 0.

- b.) Both types of networks: Transient response without computing the steady-state values as initial conditions. A set of the initial condition of analog and digital nodes at  $t = 0^{-}$  may be specified by the user.

4.) Various Waveforms for Time Domain Analyses - Pulse, pulse train, cosine, exponential, exponential cosine, piecewise linear, and dc sources.

5.) Frequency Domain Analyses of Linear SCN's - A single-frequency sinusoidal input can produce a steady-state output containing many frequency components. SWITCAP can determine all of these output frequency components for both continuous and piecewise-constant input waveforms. z-domain quantities can also be computed. Frequency-domain group delay and sensitivity analyses are also provided.

6.) Built-In Sampling Functions - Both the input and output waveforms may be sampled and held at arbitrary instants to produce the desired waveforms for time- and frequency-domain analyses of linear SCN's except for sensitivity analysis. The output waveforms may also be sampled with a train of impulse functions for z-domain analyses.

7.) Subcircuits - Subcircuits, including analog and/or digital elements, may be defined with symbolic values for capacitances, VCVS gains, clocks, and other parameters. Hierarchical use of subcircuits is allowed.

8.) Finite Resistances, Op Amp Poles, and Switch Parasitics - Finite resistance is modeled with SCN's operating at clock frequencies higher than the normal clock. These "resistors" permit the modeling of op amp poles. Capacitors are added to the switch model to represent clock feedthrough.

Chapter 9 - Switched Capacitor Circuits (6/4/01)

- © P.E. Allen, 2001

Page 9.4-18

CMOS Analog Circuit Design -

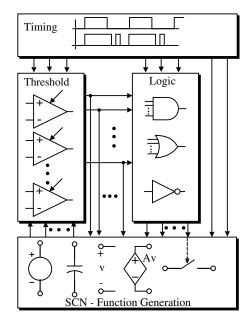

#### SWITCAP - MIXED SC/D NETWORKS

Structure of mixed SC/D networks as defined in SWITCAP2.

#### **INFO ON SWITCAP3**

Dear Prof. Allen:

Let me explain the latest regarding the development of SWITCAP3.

The current version of SWITCAP is SWITCAP2 version 1.2. It has time-domain and frequencydomain (sinusoidal stead-state, spectrum, frequency-component analyses) analyses, sensitivity analysis, group delay analysis for SCF's. It has also time-domain analysis of mixed switched-capacitor and digital networks so that you can simulate data converters including sigma-delta converters. We only have Sun and HP versions. We don't have a PC version for SWITCAP2.

We are distributing a graphic interface package for SWITCAP2 called XCAP. It has input schematic caption and postprocessing graphics. The package was developed by an outside company.

We have finished 95 percent of SWITCAP3 coding. It will include all the analyses in SWITCAP2 plus noise analysis of SCF's and time- and frequency-domain analyses of switched-current circuits that are modelled using actual MOSFET models (currently, we have BSIM3 and Level 3) and usual SCN ideal components. Although we are already running some examples, it will take a few more months to make a beta-site version available.

I hope the above information is sufficient for your purpose. If you or your students have further questions, please don't hesitate to contact me.

Regards,

Ken Suyama

Microelectronic Circuits & Systems Laboratory Department of Electrical Engineering, Columbia University 1312 S. W. Mudd Building, 500 West 120th Street, New York, NY 10027, USA TEL:212-854-6895 FAX:212-663-7203 EMAIL:suyama@elab.columbia.edu

Chapter 9 - Switched Capacitor Circuits (6/4/01)

- © P.E. Allen, 2001 -

Page 9.5-1

CMOS Analog Circuit Design -

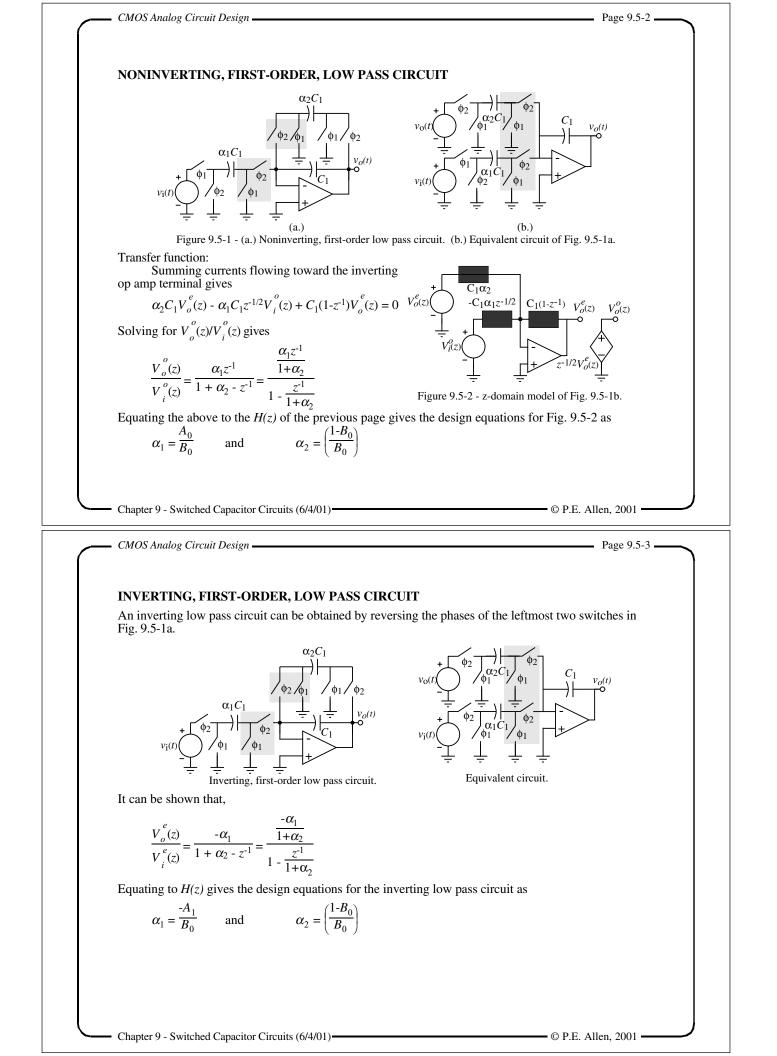

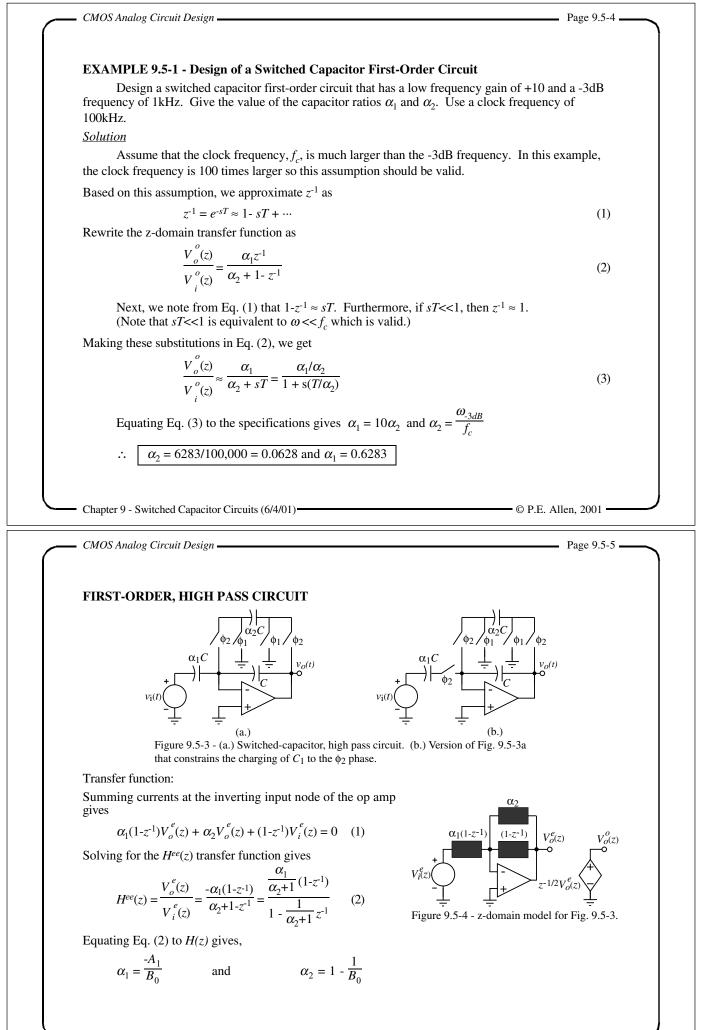

# 9.5 - FIRST-ORDER, SWITCHED CAPACITOR CIRCUITS GENERAL, FIRST-ORDER TRANSFER FUNCTIONS

A general first-order transfer function in the s-domain:

$$H(s) = \frac{sa_1 \pm a_0}{s + b_0}$$

$a_1 = 0 \implies$  Low pass,  $a_0 = 0 \implies$  High Pass,  $a_0 \neq 0$  and  $a_1 \neq 0 \implies$  All pass

Note that the zero can be in the *RHP* or *LHP*.

A general first-order transfer function in the z-domain:

$$H(z) = \frac{zA_1 \pm A_0}{z - B_0} = \frac{A_1 \pm A_0 z^{-1}}{1 - B_0 z^{-1}}$$

- © P.E. Allen, 2001 -

- © P.E. Allen, 2001 -

- © P.E. Allen, 2001

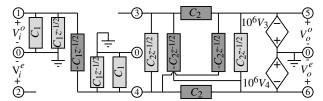

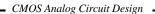

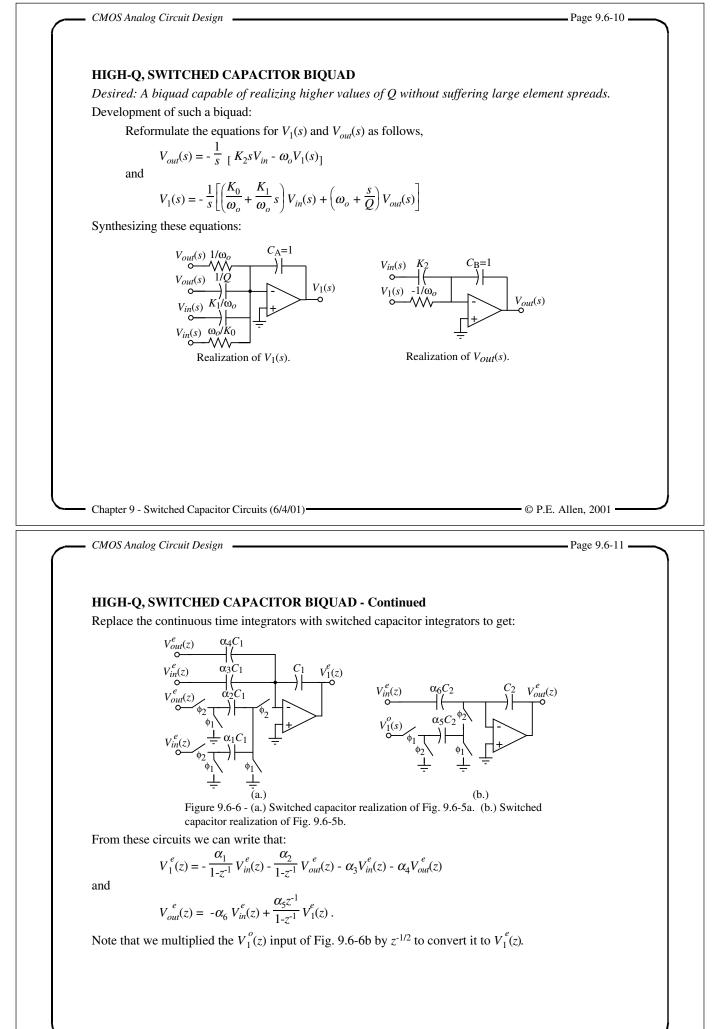

Replace the continuous time integrators with switched capacitor integrators to get:

Figure 9.6-3 - (a.) Switched capacitor realization of Fig. 9.6-2a. (b.) Switched capacitor realization of Fig. 9.6-2b.

From these circuits we can write that:

$V_1^{e}(z) = -\frac{\alpha_1}{1 - z^{-1}} V_{in}^{e}(z) - \frac{\alpha_2}{1 - z^{-1}} V_{out}^{e}(z)$

and

$$V_{out}^{e}(z) = -\alpha_3 V_{in}^{e}(z) - \frac{\alpha_4}{1 - z^1} V_{in}^{e}(z) + \frac{\alpha_5 z^{-1}}{1 - z^1} V_1^{e}(z) - \frac{\alpha_6}{1 - z^1} V_{out}^{e}(z) .$$

Note that we multiplied the  $V_1^o(z)$  input of Fig. 9.6-3b by  $z^{-1/2}$  to convert it to  $V_1^e(z)$ .

Chapter 9 - Switched Capacitor Circuits (6/4/01)-

- © P.E. Allen, 2001

CMOS Analog Circuit Design

Page 9.6-5

# LOW-Q, SWITCHED CAPACITOR BIQUAD - Continued

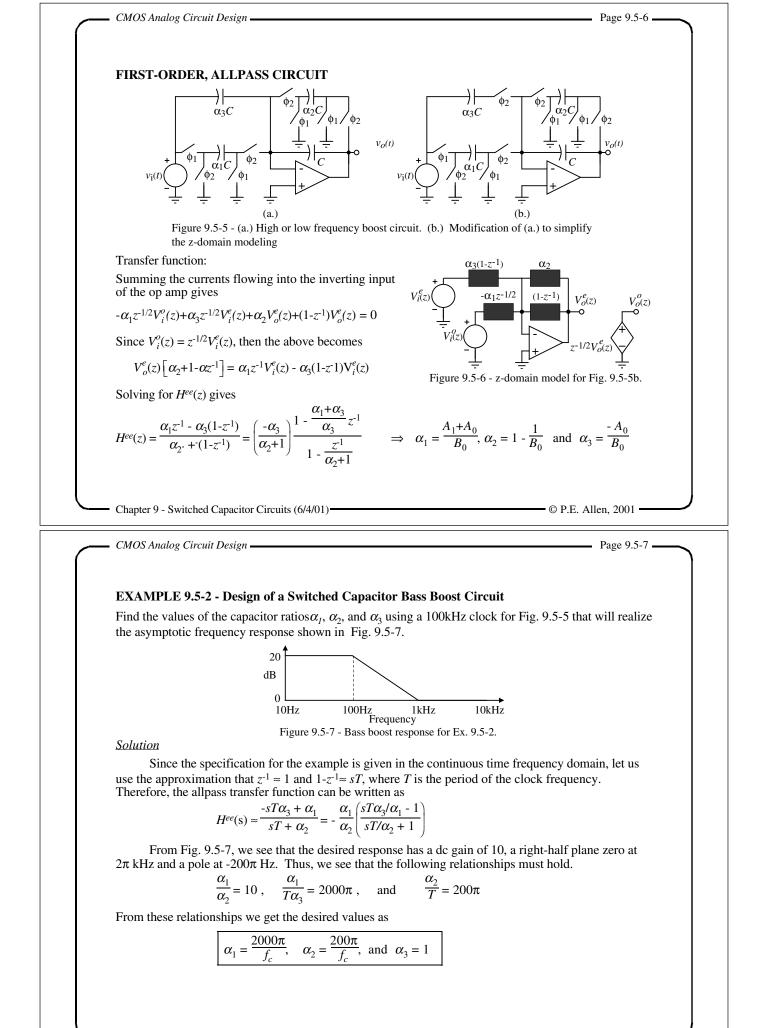

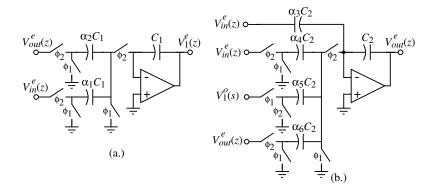

Connecting the two circuits of Fig. 9.6-3 together gives the desired, low-Q, biquad realization.

Figure 9.6-4 - Low Q, switched capacitor, biquad realization.

If we assume that  $\omega T \ll 1$ , then  $1-z^{-1} \approx sT$  and  $V_{1}^{e}(z)$  and  $V_{out}^{e}(z)$  can be approximated as

$V_1^e(s) \approx -\frac{\alpha_1}{sT} V_{in}^e(s) - \frac{\alpha_2}{sT} V_{out}^e(s) = \frac{-1}{s} \left[ \frac{\alpha_1}{T} V_{in}^e(s) + \frac{\alpha_2}{T} V_{out}^e(s) \right]$

and

$$V_{out}^{e}(s) \approx \frac{-1}{s} \left[ (\frac{\alpha_4}{T} + s\alpha_3) V_{in}^{e}(s) + \frac{\alpha_5}{T} V_1^{e}(s) + \frac{\alpha_6}{sT} V_{out}^{e}(s) \right].$$

These equations can be combined to give the transfer function,  $H^{ee}(s)$  as follows.

$$H^{ee}(s) \approx \frac{\left[\alpha_3 s^2 + \frac{s\alpha_4}{T} + \frac{\alpha_1 \alpha_5}{T^2}\right]}{s^2 + \frac{s\alpha_6}{T} + \frac{\alpha_2 \alpha_5}{T^2}}$$

CMOS Analog Circuit Design

#### Page 9.6-6

#### LOW-Q, SWITCHED CAPACITOR BIQUAD - Continued

Equating  $H^{ee}(s)$  to  $H_{a}(s)$  gives

$$\frac{\left[\alpha_{3}s^{2} + \frac{s\alpha_{4}}{T} + \frac{\alpha_{1}\alpha_{5}}{T^{2}}\right]}{s^{2} + \frac{s\alpha_{6}}{T} + \frac{\alpha_{2}\alpha_{5}}{T^{2}}} = \frac{-(K_{2}s^{2} + K_{1}s + K_{0})}{s^{2} + \frac{\omega_{o}}{Q}s + \omega_{o}^{2}}$$

which gives,

$$\alpha_1 = \frac{K_0 T}{\omega_o}, \ \alpha_2 = |\alpha_5| = \omega_o T, \ \alpha_3 = K_2, \ \alpha_4 = K_1 T, \ \text{and} \ \alpha_6 = \frac{\omega_o T}{Q} \ .$$

Largest capacitor ratio:

If Q > 1 and  $\omega_0 T \ll 1$ , the largest capacitor ratio is  $\alpha_6$ .

For this reason, the low-Q, switched capacitor biquad is restricted to Q < 5.

Sum of capacitance:

To find this value, normalize all of the capacitors connected or switched into the inverting terminal of each op amp by the smallest capacitor,  $\alpha_{min}C$ . The sum of the normalized capacitors associated with each op amp will be the sum of the capacitance connected to that op amp. Thus,

$$\Sigma C = \frac{1}{\alpha_{\min}} \sum_{i=1}^{n} \alpha_i$$

where there are n capacitors connected to the op amp inverting terminal, including the integrating capacitor.

Chapter 9 - Switched Capacitor Circuits (6/4/01)-

- © P.E. Allen, 2001

#### CMOS Analog Circuit Design

# Page 9.6-7 -

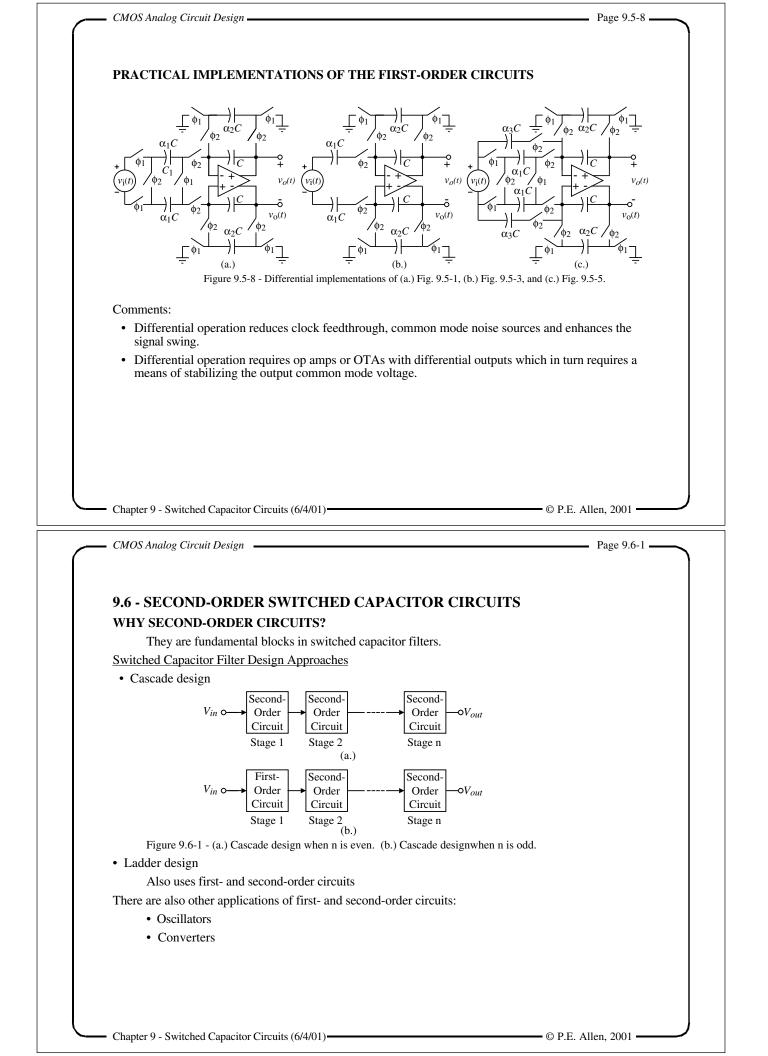

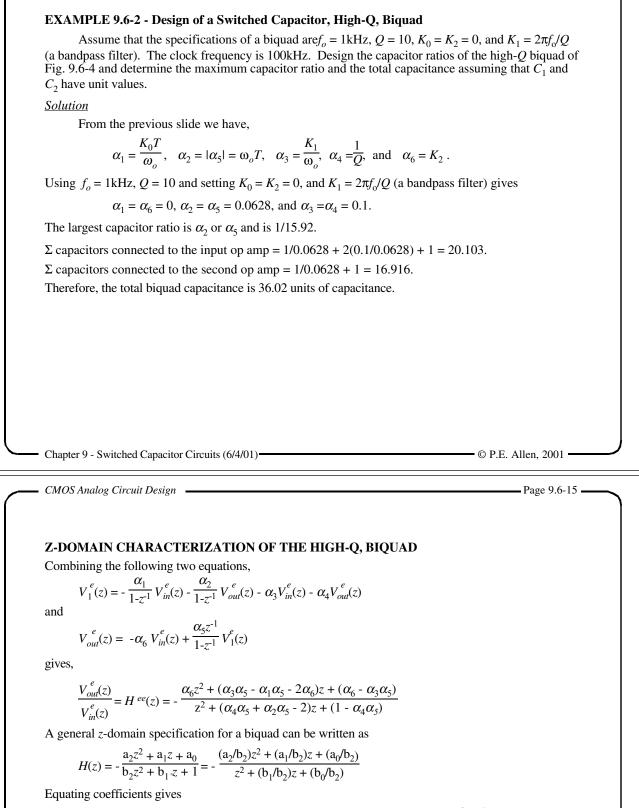

### EXAMPLE 9.6-1- Design of a Switched Capacitor, Low-Q, Biquad

Assume that the specifications of a biquad  $\operatorname{are} f_o = 1 \operatorname{kHz}$ , Q = 2,  $K_0 = K_2 = 0$ , and  $K_1 = 2\pi f_o/Q$  (a bandpass filter). The clock frequency is 100kHz. Design the capacitor ratios of Fig. 9.6-4 and determine the maximum capacitor ratio and the total capacitance assuming that  $C_1$  and  $C_2$  have unit values.

**Solution**

From the previous slide we have

$$\alpha_1 = \frac{K_0 T}{\omega_o}$$

,  $\alpha_2 = |\alpha_5| = \omega_o T$ ,  $\alpha_3 = K_2$ ,  $\alpha_4 = K_1 T$ , and  $\alpha_6 = \frac{\omega_o T}{Q}$ .

Setting  $K_0 = K_2 = 0$ , and  $K_1 = 2\pi f_0/Q$  and letting  $f_0 = 1$  kHz, Q = 2 gives

$$\alpha_1 = \alpha_3 = 0, \ \alpha_2 = \alpha_5 = 0.0628$$

, and  $\alpha_4 = \alpha_6 = 0.0314$ .

The largest capacitor ratio is  $\alpha_4$  or  $\alpha_6$  and is 1/31.83.

$\Sigma$  capacitors connected to the input op amp = 1/0.0628 + 1 = 16.916.

$\Sigma$  capacitors connected to the second op amp = 0.0628/0.0314 + 1/0.0314 + 2 = 35.85.

Therefore, the total biquad capacitance is 52.76 units of capacitance.

(Note that this number will decrease as the clock frequency becomes closer to the signal frequencies.)

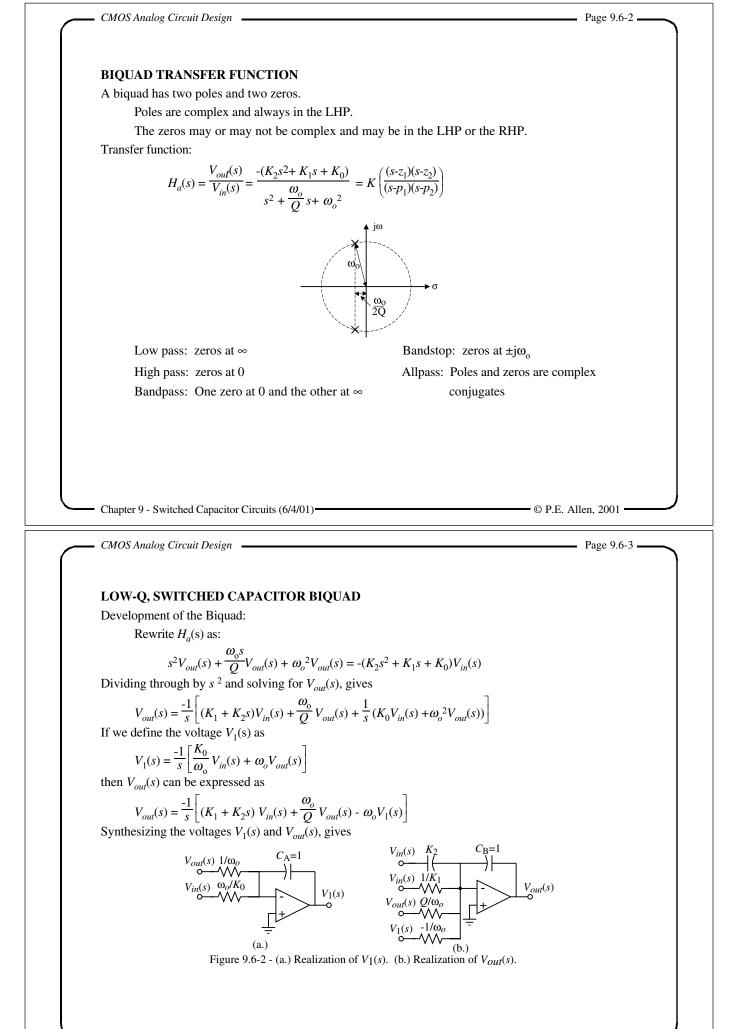

# Z-DOMAIN CHARACTERIZATION OF THE LOW-Q, BIQUAD

Combining the following two equations,

$$V_1^e(z) = -\frac{\alpha_1}{1 - z^{-1}} V_{in}^e(z) - \frac{\alpha_2}{1 - z^{-1}} V_{out}^e(z)$$

and

$$V_{out}^{e}(z) = -\alpha_3 V_{in}^{e}(z) - \frac{\alpha_4}{1 - z^{-1}} V_{in}^{e}(z) + \frac{\alpha_5 z^{-1}}{1 - z^{-1}} V_1^{e}(z) - \frac{\alpha_6}{1 - z^{-1}} V_{out}^{e}(z) \,.$$

gives,

$$\frac{V_{out}^{e}(z)}{V_{in}^{e}(z)} = H^{ee}(z) = -\frac{(\alpha_{3} + \alpha_{4})z^{2} + (\alpha_{1}\alpha_{5} - \alpha_{4} - 2\alpha_{3})z + \alpha_{3}}{(1 + \alpha_{6})z^{2} + (\alpha_{2}\alpha_{5} - \alpha_{6} - 2)z + 1}$$

A general z-domain specification for a biquad can be written as

$$H(z) = -\frac{a_2 z^2 + a_1 z + a_0}{b_2 z^2 + b_1 z + 1}$$

Equating coefficients gives

$$\alpha_3 = a_0, \ \alpha_4 = a_2 - a_0, \ \alpha_1 \alpha_5 = a_2 + a_1 + a_0, \ \alpha_6 = b_2 - 1, \ \text{and} \ \alpha_2 \alpha_5 = b_2 + b_1 + 1$$

Because there are 5 equations and 6 unknowns, an additional relationship can be introduced. One approach would be to select  $\alpha_5 = 1$  and solve for the remaining capacitor ratios. Alternately, one could let  $\alpha_2 = \alpha_5$  which makes the integrator frequency of both integrators in the feedback loop equal.

Chapter 9 - Switched Capacitor Circuits (6/4/01)-

- © P.E. Allen, 2001

Page 9.6-9

Page 9.6-8

CMOS Analog Circuit Design -

# VOLTAGE SCALING

It is desirable to keep the amplitudes of the output voltages of the two op amps approximately equal over the frequency range of interest. This can be done by voltage scaling.

If the voltage at the output node of an op amp in a switched capacitor circuit is to be scaled by a factor of k, then all switched and unswitched capacitors connected to that output node must be scaled by a factor of 1/k.

For example,

The charge associated with  $v_1$  is:

$Q(v_1) = C_1 v_1 + \alpha_2 C_2 v_1$

Suppose we wish to scale the value of  $v_1$  by  $k_1$  so that  $v_1' = k_1 v_1$ . Therefore,

$$Q(v_1') = C_1 v_1' + \alpha_2 C_2 v_1' = C_1 k_1 v_1 + \alpha_2 C_2 k_1 v_2$$

But,  $Q(v_1) = Q(v_1')$  so that  $C_1' = C_1/k_1$  and  $C_2' = C_2/k_1$ .

This scaling is based on keeping the total charge associated with a node constant. The choice above of  $\alpha_2 = \alpha_5$  results in a near-optimally scaled dynamic range realization.

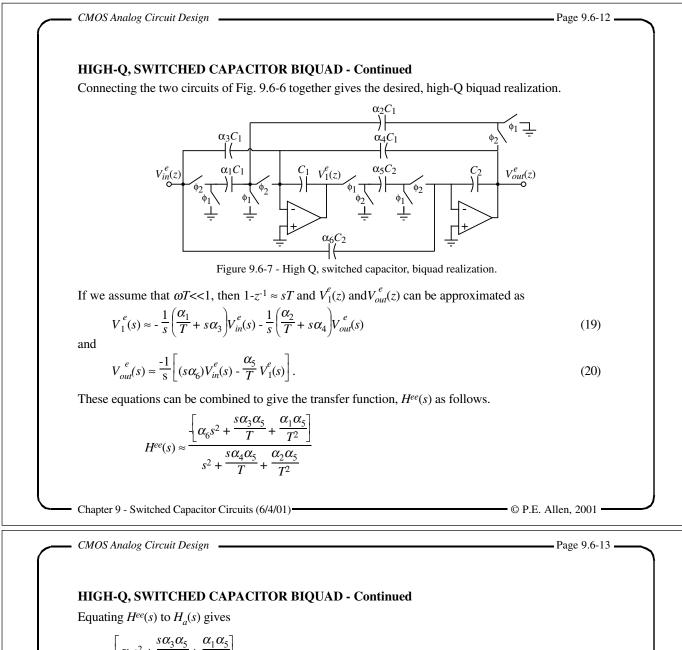

$$\frac{\left\lfloor\frac{\alpha_{6}s^{2}+\overline{T}+\overline{T}^{2}\right\rfloor}{s^{2}+\frac{s\alpha_{4}\alpha_{5}}{T}+\frac{\alpha_{2}\alpha_{5}}{T^{2}}}=\frac{-(K_{2}s_{2}+K_{1}s+K_{0})}{s^{2}+\frac{\omega_{o}}{Q}s+\omega_{o}^{2}}$$

which gives,

$$\alpha_1 = \frac{K_0 T}{\omega_o}$$

,  $\alpha_2 = |\alpha_5| = \omega_o T$ ,  $\alpha_3 = \frac{K_1}{\omega_o}$ ,  $\alpha_4 = \frac{1}{Q}$ , and  $\alpha_6 = K_2$ .

Largest capacitor ratio:

If Q > 1 and  $\omega_0 T \ll 1$ , the largest capacitor ratio is  $\alpha_2(\alpha_5)$  or  $\alpha_4$  depending on the values of Q and  $\omega_0 T$ .

CMOS Analog Circuit Design

#### Page 9.6-14

$$\alpha_6 = \frac{a_2}{b_2}, \ \alpha_3 \alpha_5 = \frac{a_2 - a_0}{b_2}, \ \alpha_1 \alpha_5 = \frac{a_2 + a_1 + a_0}{b_2}, \ \alpha_4 \alpha_5 = 1 - \frac{1}{b_2} \text{ and } \alpha_2 \alpha_5 = 1 + \frac{b_1 + 1}{2}$$

Because there are 5 equations and 6 unknowns, an additional relationship can be introduced. One approach would be to select  $\alpha_5 = 1$  and solve for the remaining capacitor ratios. Alternately, one could let  $\alpha_2 = \alpha_5$  which makes the integrator frequency of both integrators in the feedback loop equal.

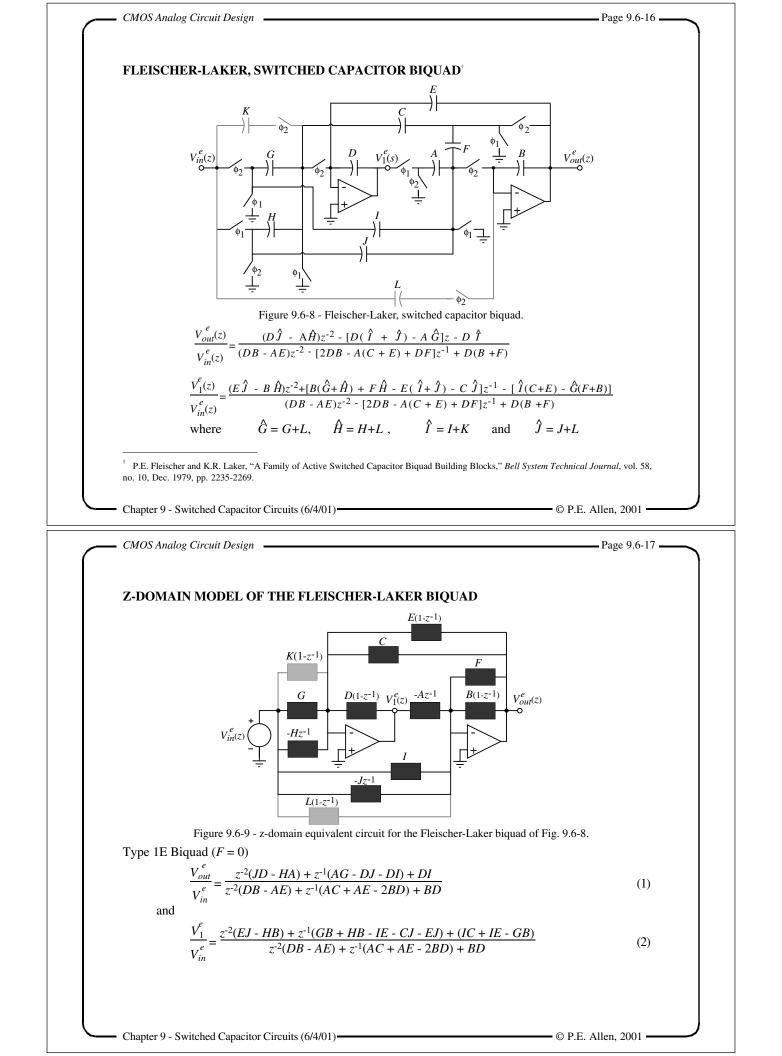

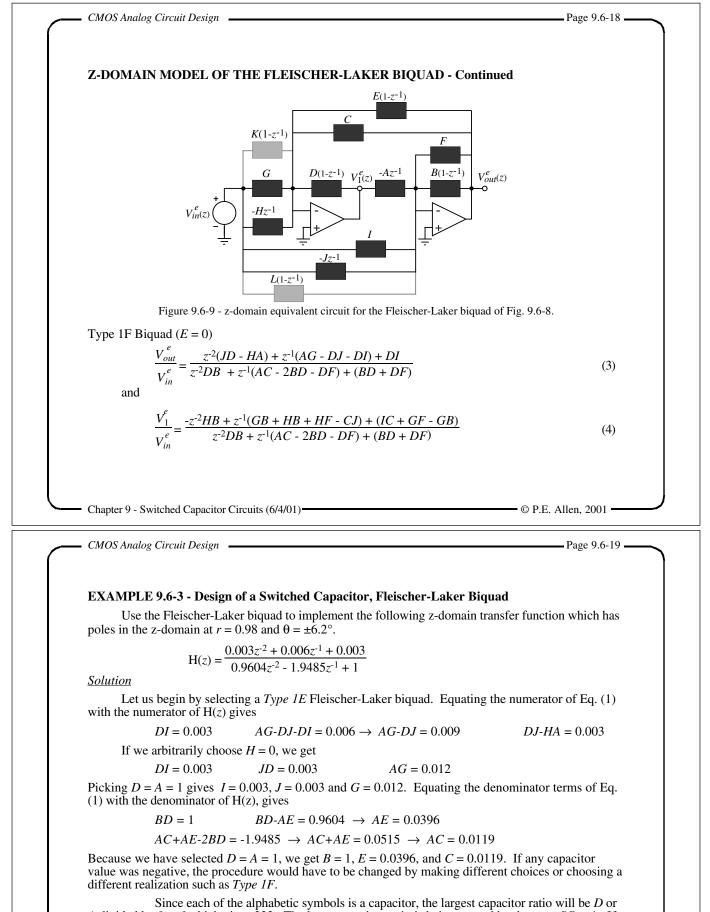

Since each of the alphabetic symbols is a capacitor, the largest capacitor ratio will be D or A divided by I or J which gives 333. The large capacitor ratio is being caused by the term BD = 1. If we switch to the *Type IF*, the term BD = 0.9604 will cause large capacitor ratios. This example is a case where both the E and F capacitors are needed to maintain a smaller capacitor ratio.

CMOS Analog Circuit Design \_

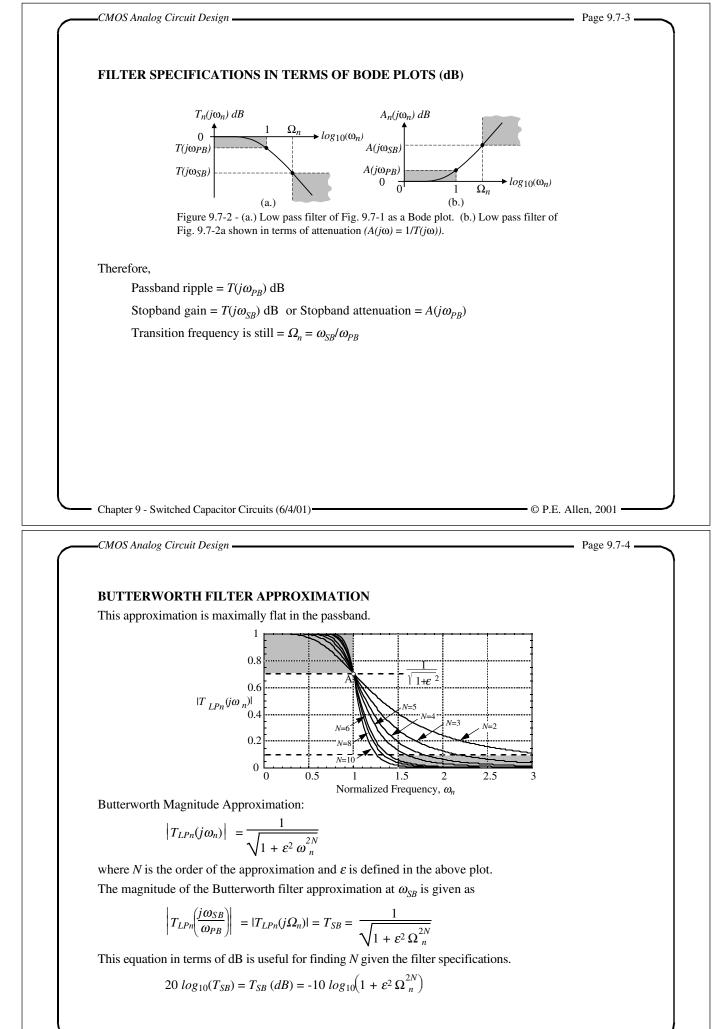

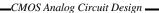

# **EXAMPLE 9.7-1 - Determining the Order of A Butterworth Filter Approximation**

Assume that a normalized, low-pass filter is specified as  $T_{PB} = -3dB$ ,  $T_{SB} = -20 dB$ , and  $\Omega_n = 1.5$ . Find the smallest integer value of N of the Butterworth filter approximation which will satisfy this specification.

<u>Solution</u>

$T_{PB} = -3dB$  corresponds to  $T_{PB} = 0.707$  which implies that  $\varepsilon = 1$ . Thus, substituting  $\varepsilon = 1$  and  $\Omega_n = 1.5$  into the equation at the bottom of the previous slide gives

$T_{SB}(dB) = -10 \log_{10}(1 + 1.5^{2N})$

Substituting values of N into this equation gives,

$T_{SB} = -7.83 \ dB \ for \ N = 2 \\ -10.93 \ dB \ for \ N = 3 \\ -14.25 \ dB \ for \ N = 4 \\ -17.68 \ dB \ for \ N = 5 \\ -21.16 \ dB \ for \ N = 6.$

Thus, *N* must be 6 or greater to meet the filter specification.

Chapter 9 - Switched Capacitor Circuits (6/4/01)-

- © P.E. Allen, 2001

CMOS Analog Circuit Design -

# Page 9.7-6 -

Page 9.7-5

## POLES AND QUADRATIC FACTORS OF BUTTERWORTH FUNCTIONS

Table 9.7-1 - Pole locations and quadratic factors  $(s_n^2 + a_1 s_n + 1)$  of normalized, low pass Butterworth functions for  $\varepsilon = 1$ . Odd orders have a product  $(s_n+1)$ .

| N  | Poles                                           | $a_1$ coefficient |

|----|-------------------------------------------------|-------------------|

| 2  | $-0.70711 \pm j0.70711$                         | 1.41421           |

| 3  | $-0.50000 \pm j0.86603$                         | 1.00000           |

| 4  | -0.38268 ± j0.92388                             | 0.76536           |

|    | -0.92388 ± j0.38268                             | 1.84776           |

| 5  | $-0.30902 \pm j0.95106$                         | 0.61804           |

|    | $-0.80902 \pm j0.58779$                         | 1.61804           |

| 6  | $-0.25882 \pm j0.96593$ $-0.96593 \pm j0.25882$ | 0.51764 1.93186   |

|    | $-0.70711 \pm j0.70711$                         | 1.41421           |

| 7  | $-0.22252 \pm j0.97493$ $-0.90097 \pm j0.43388$ | 0.44505 1.80194   |

|    | $-0.62349 \pm j0.78183$                         | 1.24698           |

| 8  | $-0.19509 \pm j0.98079$ $-0.83147 \pm j0.55557$ | 0.39018 1.66294   |

|    | $-0.55557 \pm j0.83147$ $-0.98079 \pm j0.19509$ | 1.11114 1.96158   |

| 9  | $-0.17365 \pm j0.98481$ $-0.76604 \pm j0.64279$ | 0.34730 1.53208   |

|    | $-0.50000 \pm j0.86603$ $-0.93969 \pm j0.34202$ | 1.00000 1.87938   |

| 10 | $-0.15643 \pm j0.98769 -0.89101 \pm j0.45399$   | 0.31286 1.78202   |

|    | $-0.45399 \pm j0.89101$ $-0.98769 \pm j0.15643$ | 0.90798 1.97538   |

|    | -0.70711 ± j0.70711                             | 1.41421           |

- © P.E. Allen, 2001 -

#### Page 9.7-7

Find the roots for a Butterworth approximation with  $\varepsilon = 1$  for N = 5. **Solution**

For N = 5, the following first- and second-order products are obtained from Table 9.7-1

$$T_{LPn}(s_n) = T_1(s_n)T_2(s_n)T_3(s_n) = \left(\frac{1}{s_n+1}\right)\left(\frac{1}{s_n^2+0.6180s_n+1}\right)\left(\frac{1}{s_n^2+1.6180s_n+1}\right)$$

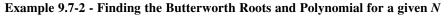

Illustration of the individual magnitude contributions of each product of  $T_{LPn}(s_n)$ .

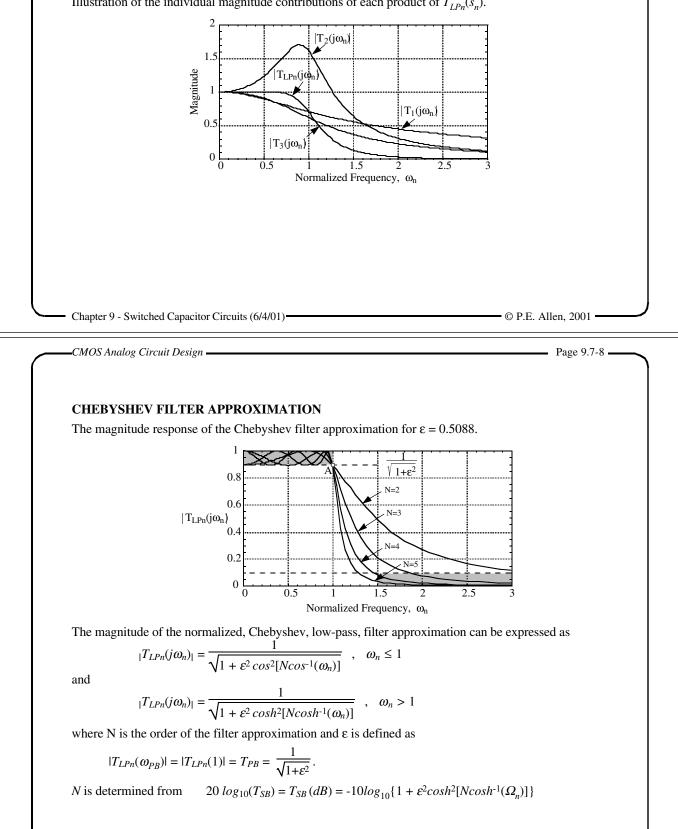

### **EXAMPLE 9.7-3** - Determining the Order of A Chebyshev Filter Approximation

Repeat Ex. 9.7-1 for the Chebyshev filter approximation.

<u>Solution</u>

In Ex. 9.7-2,  $\varepsilon = 1$  which means the ripple width is 3 *dB* or  $T_{PB} = 0.707$ . Now we substitute  $\varepsilon = 1$  into

$$20 \log_{10}(T_{SB}) = T_{SB}(dB) = -10 \log_{10}\{1 + \varepsilon^2 \cosh^2[N \cosh^{-1}(\Omega_n)]\}$$

and find the value of N which satisfies  $T_{SB} = -20dB$ .

For N = 2,  $\rightarrow T_{SB} = -11.22 \ dB$ . For N = 3,  $\rightarrow T_{SB} = -19.14 \ dB$ . For N = 4,  $\rightarrow T_{SB} = -27.43 \ dB$ .

Thus N = 4 must be used although N = 3 almost satisfies the specifications. This result compares with N = 6 for the Butterworth approximation.

Chapter 9 - Switched Capacitor Circuits (6/4/01)

© P.E. Allen, 2001

CMOS Analog Circuit Design -

# Page 9.7-10

#### POLES AND QUADRATIC FACTORS OF CHEBYSHEV FUNCTIONS

Table 9.7-2 - Pole locations and quadratic factors  $(a_0 + a_1s_n + s_n^2)$  of normalized, low pass Chebyshev functions for  $\varepsilon = 0.5088$  (1*dB*).

| N | Normalized Pole         | $a_0$   | <i>a</i> <sub>1</sub> |

|---|-------------------------|---------|-----------------------|

|   | Locations               |         |                       |

| 2 | -0.54887 ± j0.89513     | 1.10251 | 1.09773               |

| 3 | -0.24709 ± j0.96600     | 0.99420 | 0.49417               |

|   | -0.49417                |         |                       |

| 4 | -0.13954 ± j0.98338     | 0.98650 | 0.27907               |

|   | -0.33687 ± j0.40733     | 0.27940 | 0.67374               |

| 5 | -0.08946 ± j0.99011     | 0.98831 | 0.17892               |

|   | $-0.23421 \pm j0.61192$ | 0.42930 | 0.46841               |

|   | -0.28949                |         |                       |

| 6 | $-0.06218 \pm j0.99341$ | 0.99073 | 0.12436               |

|   | -0.16988 ± j0.72723     | 0.55772 | 0.33976               |

|   | $-0.23206 \pm j0.26618$ | 0.12471 | 0.46413               |

| 7 | -0.04571 ± j0.99528     | 0.99268 | 0.09142               |

|   | $-0.12807 \pm j0.79816$ | 0.65346 | 0.25615               |

|   | -0.18507 ± j0.44294     | 0.23045 | 0.37014               |

|   | -0.20541                |         |                       |

# EXAMPLE 9.7-4 - Finding the Chebyshev Roots for a given N

Find the roots for the Chebyshev approximation with  $\varepsilon = 1$  for N = 5. **Solution**

For N = 5, we get the following quadratic factors which give the transfer function as

$$T_{LPn}(s_n) = T_1(s_n)T_2(s_n)T_3(s_n) = \left(\frac{0.2895}{s_n + 0.2895}\right) \left(\frac{0.9883}{s_n^2 + 0.1789s_n + 0.9883}\right) \left(\frac{0.4293}{s_n^2 + 0.4684s_n + 0.4293}\right).$$

Chapter 9 - Switched Capacitor Circuits (6/4/01) \_\_\_\_\_ - © P.E. Allen, 2001 -

- Page 9.7-12 -

#### CMOS Analog Circuit Design -

# **OTHER APPROXIMATIONS**

Thomson Filters - Maximally flat magnitude and linear phase<sup>1</sup>

Elliptic Filters - Ripple both in the passband and stopband, the smallest transition region of all filters.<sup>2</sup>

An excellent collection of filter approximations and data is found in A.I. Zverev, Handbook of Filter Synthesis, John Wiley & Sons, Inc., New York, 1967.

W.E. Thomson, "Delay Networks Having Maximally Flat Frequency Characteristics," Proc. IEEE, part 3, vol. 96, Nov. 1949, pp. 487-490. 2

W. Cauer, Synthesis of Linear Communication Networks, McGraw-Hill Book Co., New York, NY, 1958.

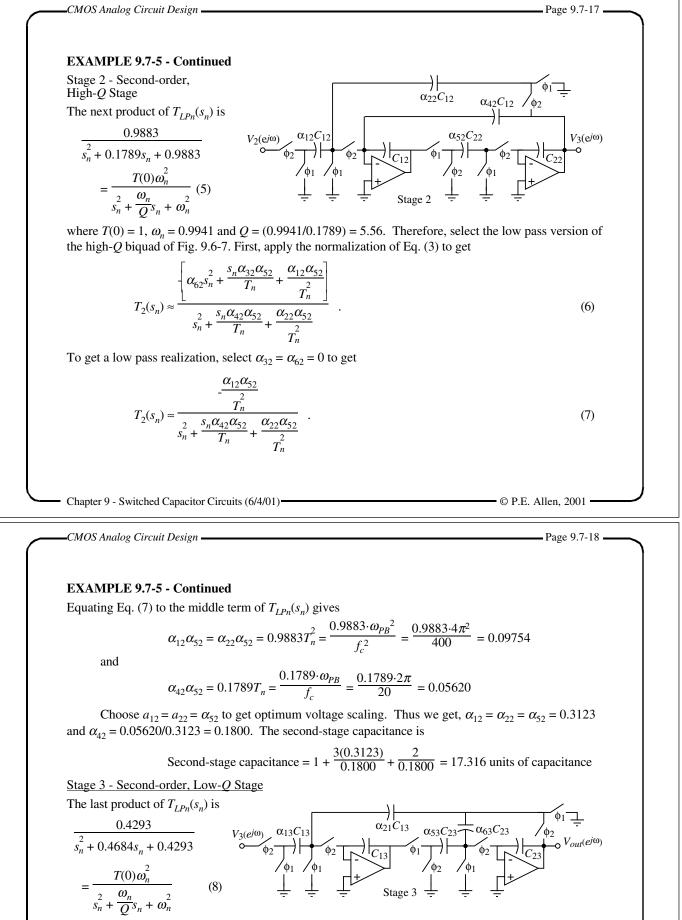

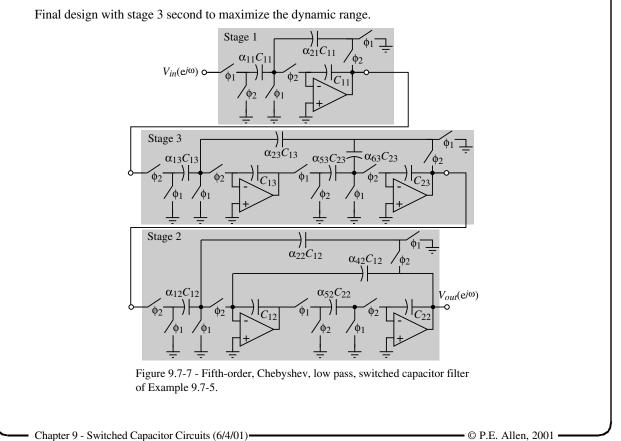

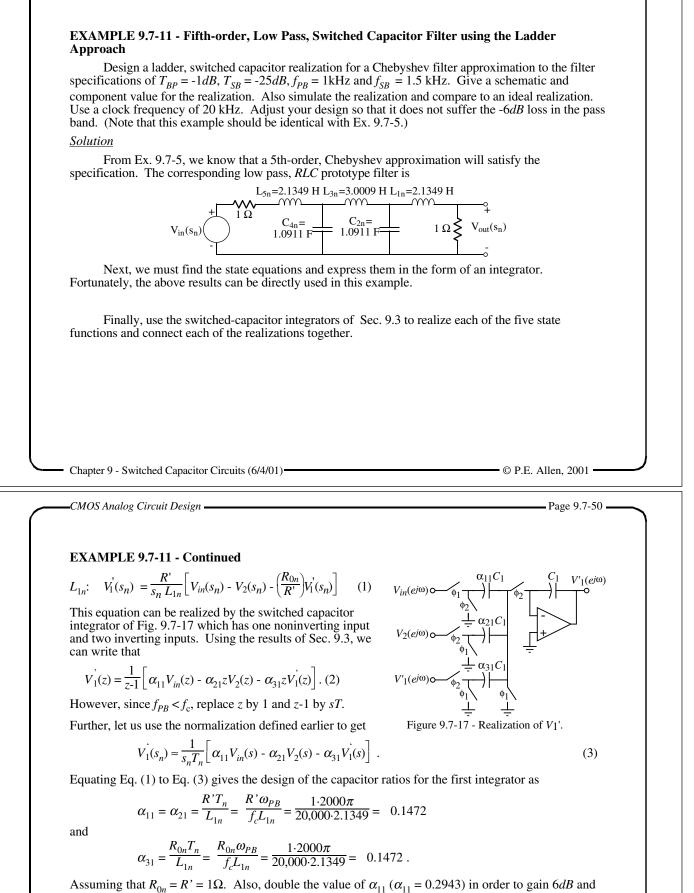

# EXAMPLE 9.7-5 - Fifth-order, Low Pass, Switched Capacitor Filter using the Cascade Approach

Design a cascade, switched capacitor realization for a Chebyshev filter approximation to the filter specifications of  $T_{PB} = -1dB$ ,  $T_{SB} = -25dB$ ,  $f_{PB} = 1$ kHz and  $f_{SB} = 1.5$ kHz. Give a schematic and component value for the realization. Also simulate the realization and compare to an ideal realization. Use a clock frequency of 20kHz.

#### <u>Solution</u>

First we see that  $\Omega_n = 1.5$ . Next, recall that when  $T_{PB} = -1dB$  that this corresponds to  $\varepsilon = 0.5088$ . We find that N = 5 satisfies the specifications ( $T_{SB} = -29.9dB$ ). Using the results of Ex. 9.7-4, we may write  $T_{LPn}(s_n)$  as

$$T_{LPn}(s_n) = \left(\frac{0.2895}{s_n + 0.2895}\right) \left(\frac{0.9883}{s_n^2 + 0.1789s_n + 0.9883}\right) \left(\frac{0.4293}{s_n^2 + 0.4684s_n + 0.4293}\right).$$

(1)

Next, we design each of the three stages individually.

Chapter 9 - Switched Capacitor Circuits (6/4/01)-

- © P.E. Allen, 2001

Page 9.7-16

# CMOS Analog Circuit Design —

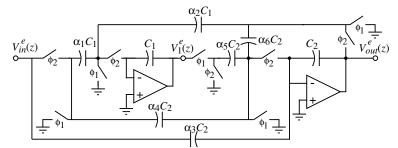

# **EXAMPLE 9.7-5 - Continued**

Stage 1 - First-order Stage

Let us select Fig. 9.5-1 to realize the first-order stage. We will assume that  $f_c$  is much greater than  $f_{BP}$  (i.e. 100) and use Eq. (10) of Sec. 9.5 repeated below to accomplish the design.

$$V_{in}(\underline{e^{j\omega}}) \underbrace{ \begin{array}{c} \alpha_{11}C_{11} \\ \phi_{1} \end{array}}_{\varphi_{2}} \underbrace{ \begin{array}{c} \alpha_{21}C_{11} \\ \phi_{2} \end{array}}_{\varphi_{2}} \underbrace{ \begin{array}{c} \alpha_{2}C_{1} \end{array}}_{\varphi_{$$

Note that we have used the second subscript 1 to denote the first stage. Before we can use this equation we must normalize the sT factor. This normalization is accomplished by

$$sT = \left(\frac{s}{\omega_{PB}}\right) \cdot (\omega_{PB}T) = s_n T_n .$$

(3)

(2)

Therefore, Eq. (2) can be written as

$T_1(s) \approx \frac{\alpha_{11}/\alpha_{21}}{1 + s(T/\alpha_{21})}$

$$T_1(s_n) \approx \frac{\alpha_{11}/\alpha_{21}}{1 + s_n(T_n/\alpha_{21})} = \frac{\alpha_{11}/T_n}{s_n + \alpha_{21}/T_n}$$

(4)

where  $\alpha_{11} = C_{11}/C$  and  $\alpha_{21} = C_{21}/C$ . Equating Eq. (4) to the first term in  $T_{LPn}(s_n)$  gives the design of Fig. 9.5-1 as

$$\alpha_{21} = \alpha_{11} = 0.2895T_n = \frac{0.2895 \cdot \omega_{PB}}{f_c} = \frac{0.2895 \cdot 2000\pi}{20,000} = 0.0909$$

The sum of capacitances for the first stage is

First-stage capacitance =  $2 + \frac{1}{0.0909} = 13$  units of capacitance

where we see that T(0) = 1,  $\omega_n = 0.6552$  and Q = (0.6552/0.4684) = 1.3988. Therefore, select the low pass version of the low-Q biquad. First, apply the normalization of Eq. (3) to get

CMOS Analog Circuit Design \_

# **EXAMPLE 9.7-5 - Continued**

$$T_{3}(s_{n}) \approx \frac{\left[\alpha_{33}s_{n}^{2} + \frac{s_{n}\alpha_{43}}{T_{n}} + \frac{\alpha_{13}\alpha_{53}}{T_{n}^{2}}\right]}{s_{n}^{2} + \frac{s_{n}\alpha_{63}}{T_{n}} + \frac{\alpha_{23}\alpha_{53}}{T_{n}^{2}}}$$

(9)

To get a low pass realization, select  $\alpha_{33} = \alpha_{43} = 0$  to get

$$T_{3}(s_{n}) \approx \frac{-\frac{\alpha_{13}\alpha_{53}}{T_{n}^{2}}}{s_{n}^{2} + \frac{s_{n}\alpha_{63}}{T_{n}} + \frac{\alpha_{23}\alpha_{53}}{T_{n}^{2}}} \quad .$$

(10)

Equating Eq. (10) to the last term of  $T_{LPn}(s_n)$  gives

$$\alpha_{13}\alpha_{53} = \alpha_{23}\alpha_{53} = 0.4293T_n^2 = \frac{0.4293 \cdot \omega_{PB}^2}{f_c^2} = \frac{0.4293 \cdot 4\pi^2}{400} = 0.04237$$

and

$$\alpha_{63} = 0.4684T_n = \frac{0.4684 \cdot \omega_{PB}}{f_c} = \frac{0.4684 \cdot 2\pi}{20} = 0.1472$$

Choose  $a_{13} = a_{23} = \alpha_{53}$  to get optimum voltage scaling. Thus,  $\alpha_{13} = \alpha_{23} = \alpha_{53} = 0.2058$  and  $\alpha_{63} = 0.1472$ . The third-stage capacitance is

Third-stage capacitance =  $1 + \frac{3(0.2058)}{0.1472} + \frac{2}{0.1472} = 18.78$  units of capacitance

The total capacitance of this design is 13 + 17.32 + 18.78 = 49.10 units of capacitance.

Chapter 9 - Switched Capacitor Circuits (6/4/01)-

Page 9.7-20

- © P.E. Allen, 2001

Page 9.7-19

CMOS Analog Circuit Design -

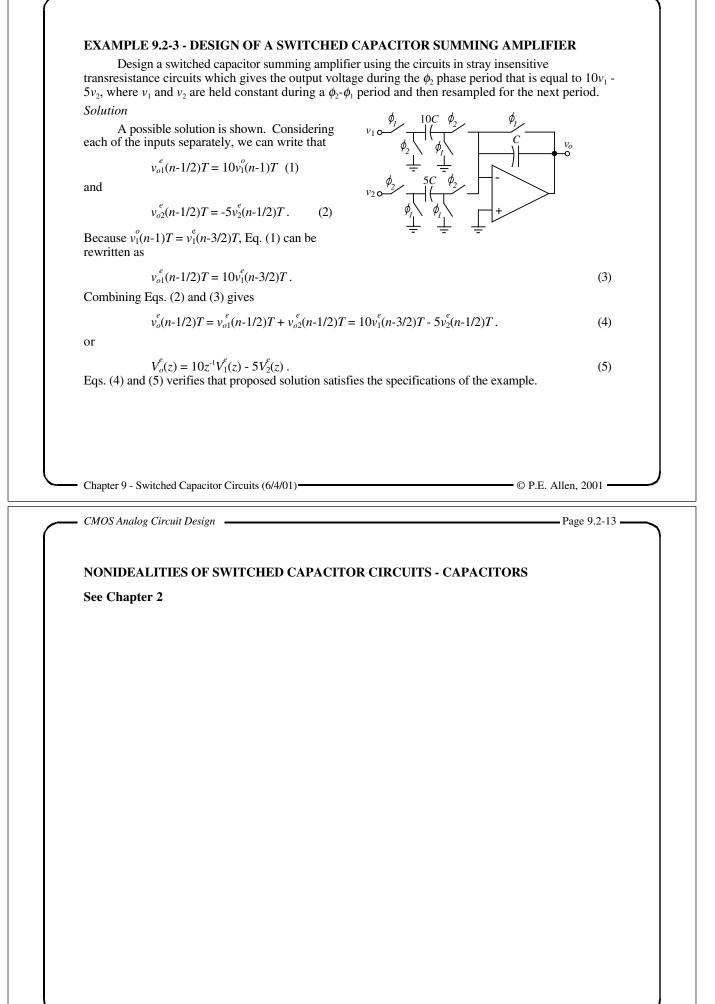

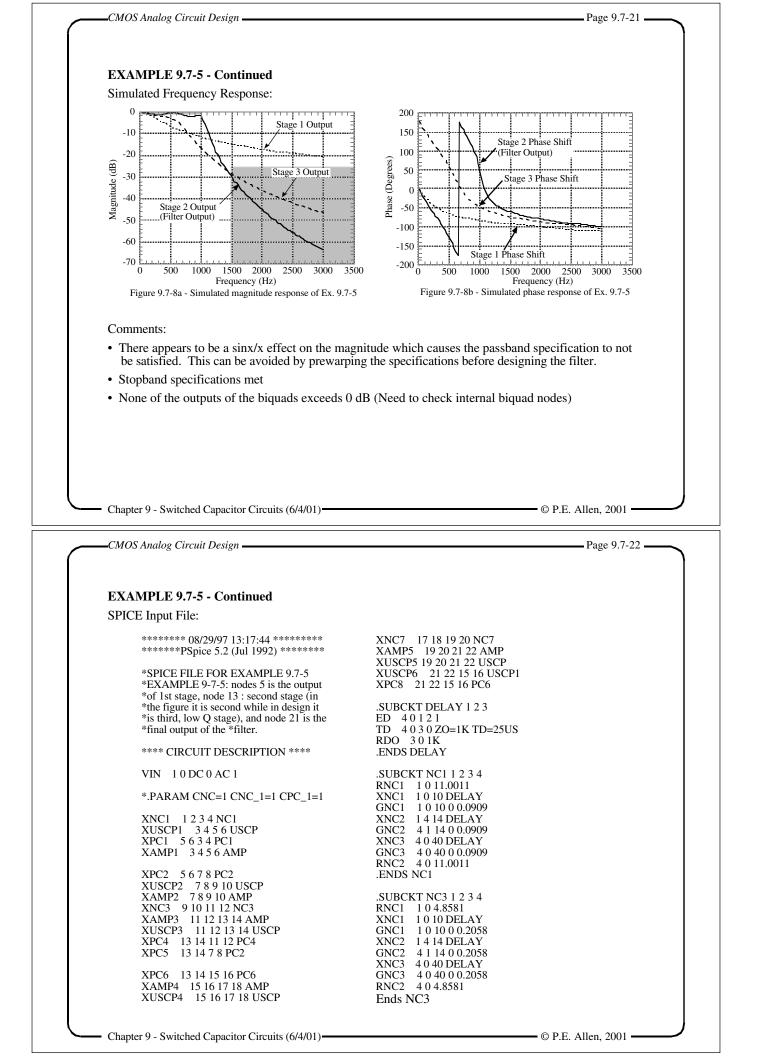

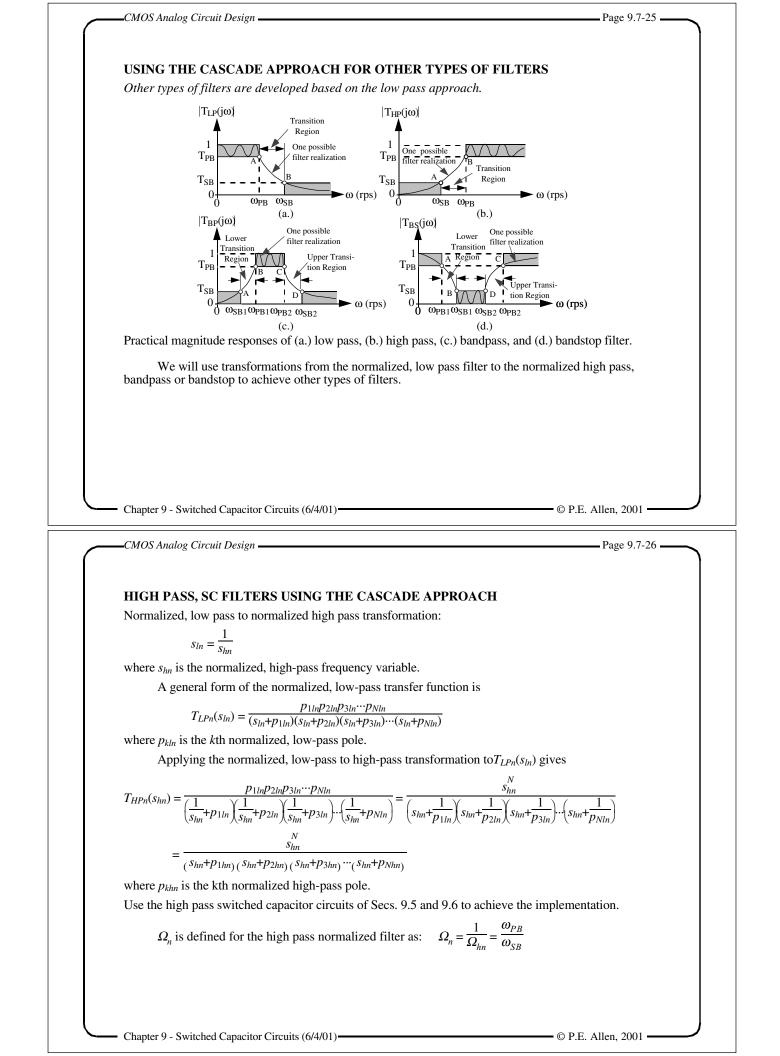

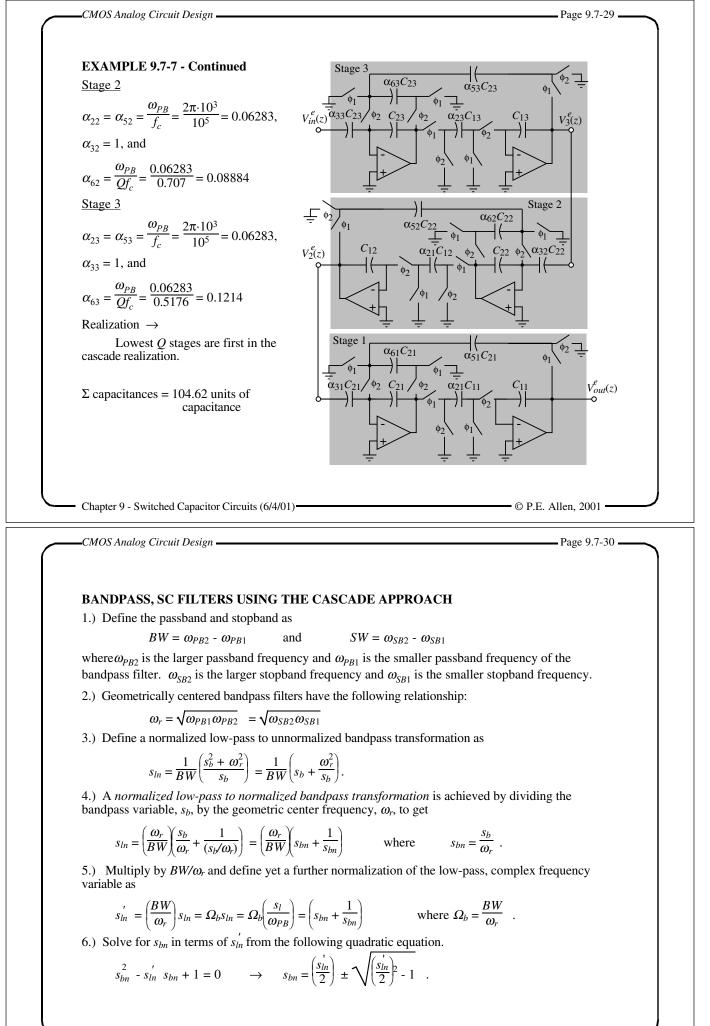

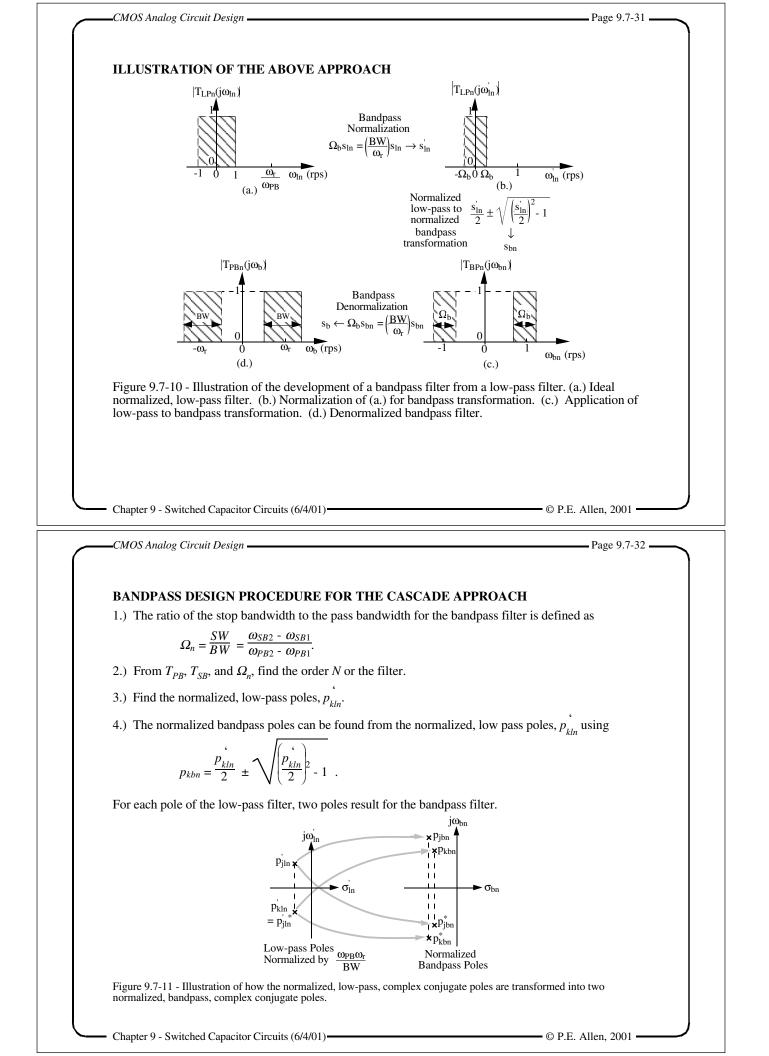

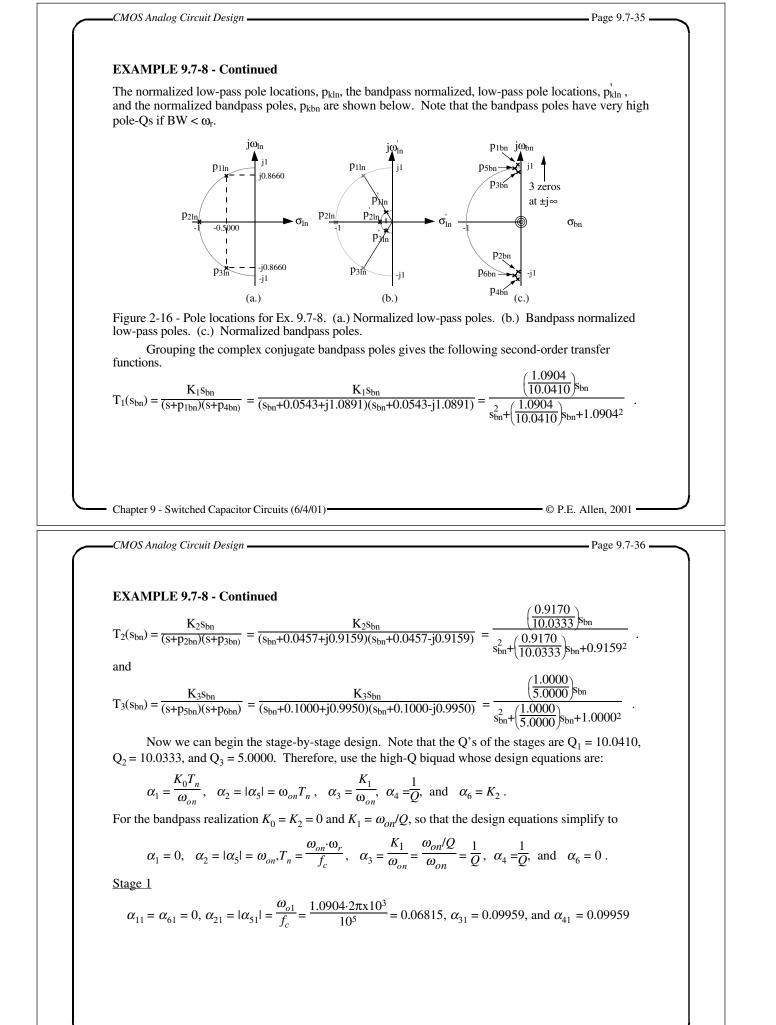

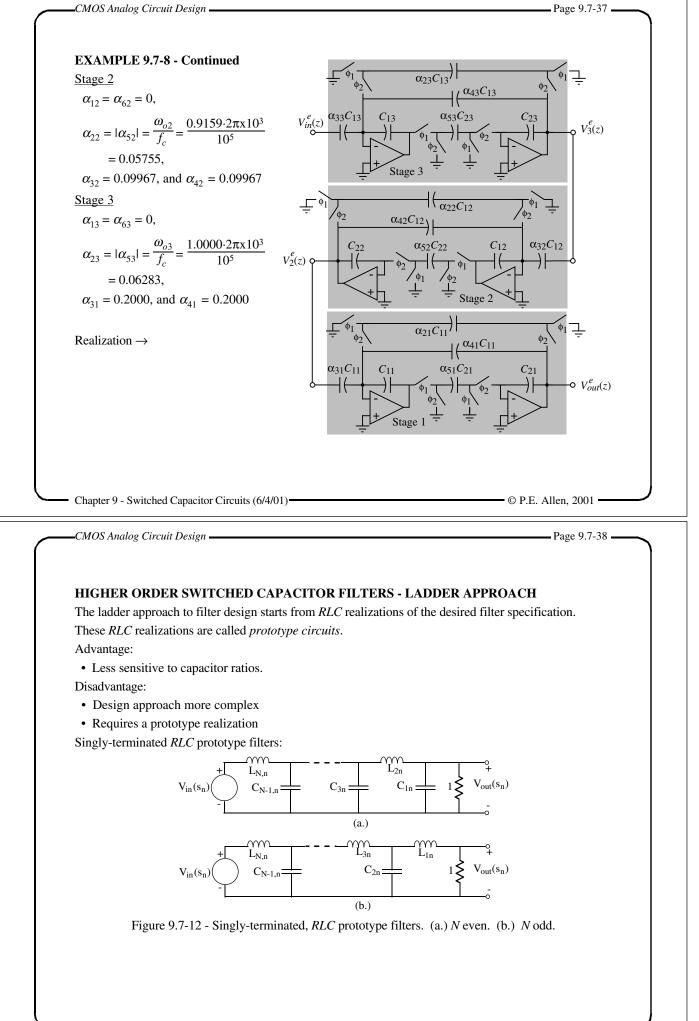

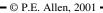

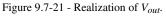

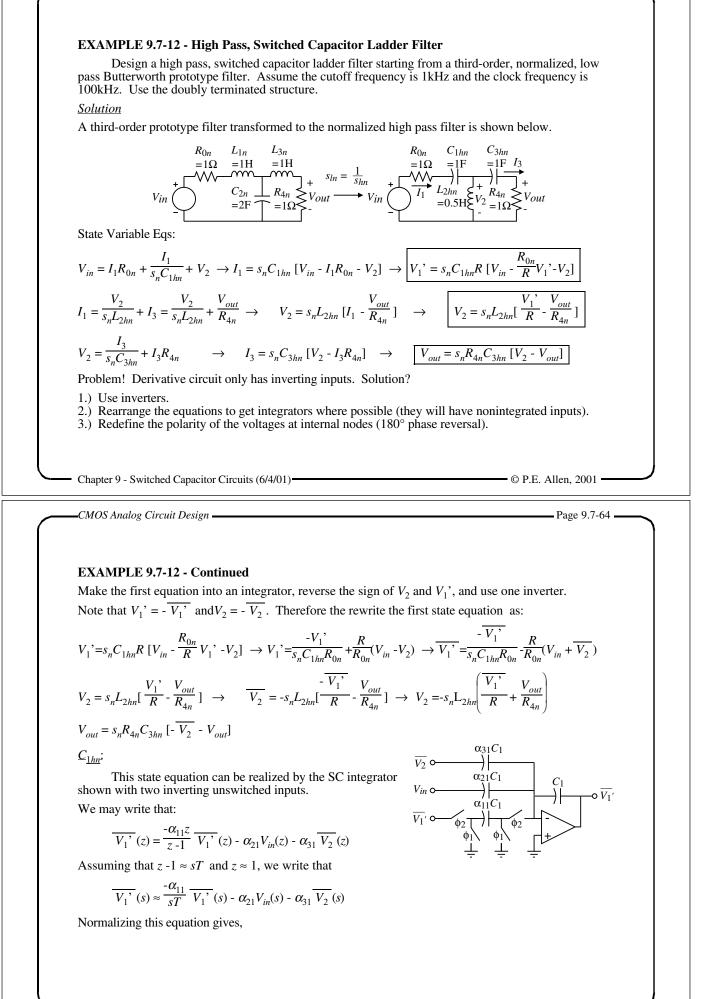

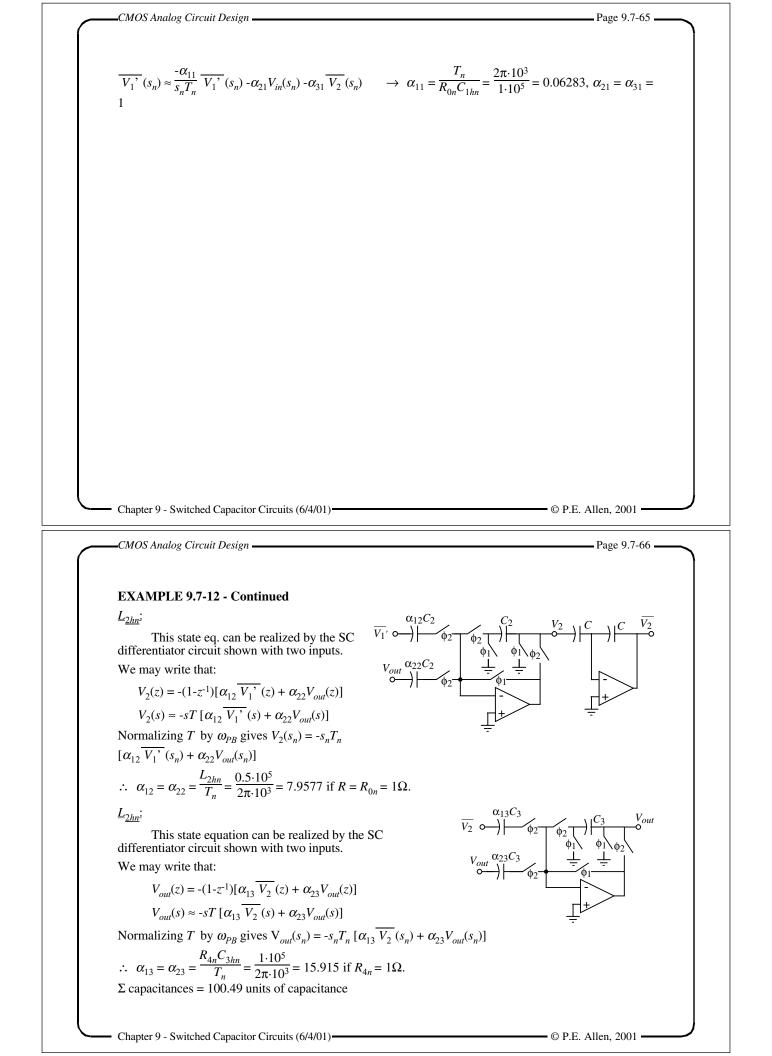

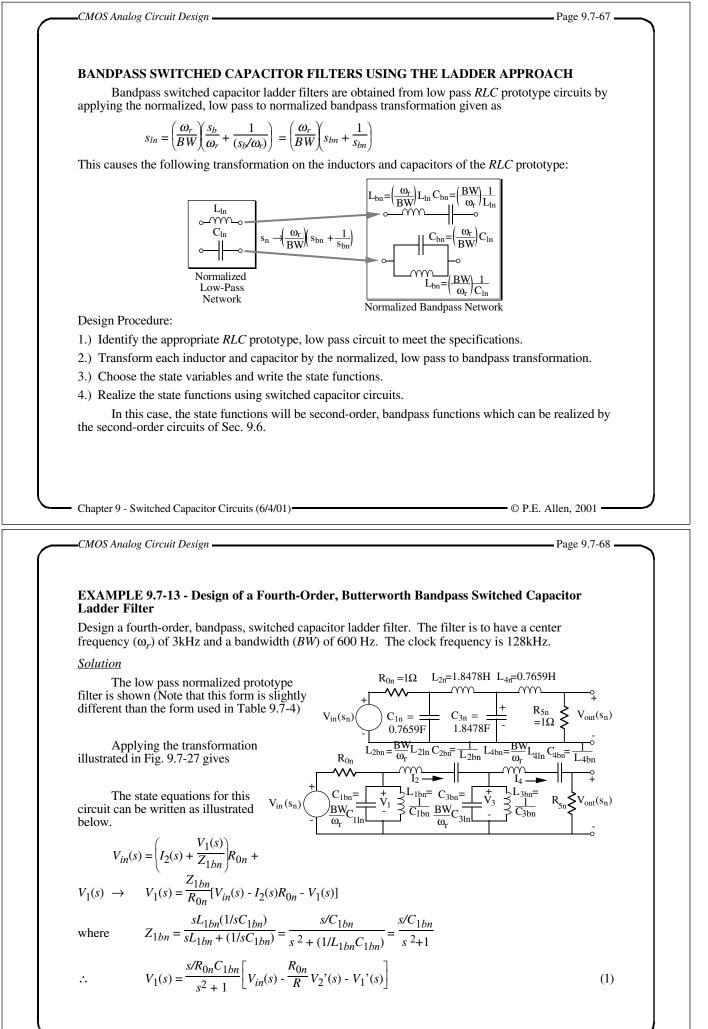

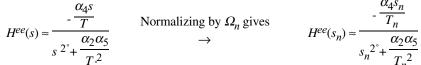

# **EXAMPLE 9.7-5 - Continued**