## Types of D/A Converters

| DAC Type        | Advantage                              | Disadvantage                                   |

|-----------------|----------------------------------------|------------------------------------------------|

| Current Scaling | Fast, insensitive to switch parasitics | Large element spread,<br>nonmonotonic          |

| Voltage Scaling | Monotonic, equal resistors             | Large area, sensitive to parasitic capacitance |

| Charge Scaling  | Fast, good accuracy                    | Large element spread,<br>nonmonotonic          |

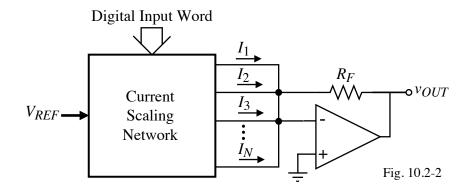

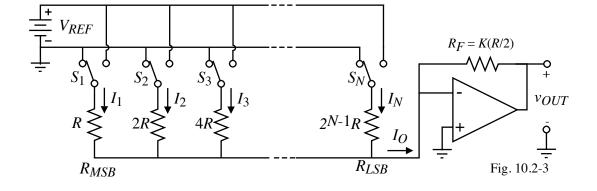

### Current Scaling D/As

The output voltage can be expressed as

$$V_{out} = R_f (I_1 + I_2 + I_3 + ... + I_N)$$

where the currents *I*1, *I*2, *I*3, ... are binary weighted currents.

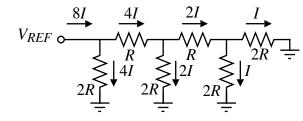

### D/As built from R-2R Ladders

The output voltage can be expressed as

$$V_{out} = R_f (I_1 + I_2 + I_3 + \dots + I_N)$$

where the currents *I*1, *I*2, *I*3, ... are binary weighted currents.

"The resistance seen to the right of any of the vertical 2R resistors is 2R."

Not monotonic

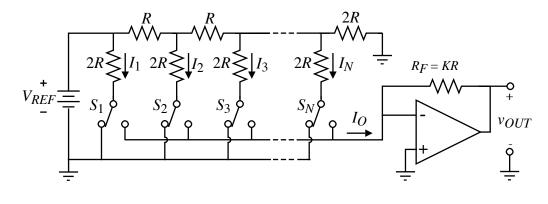

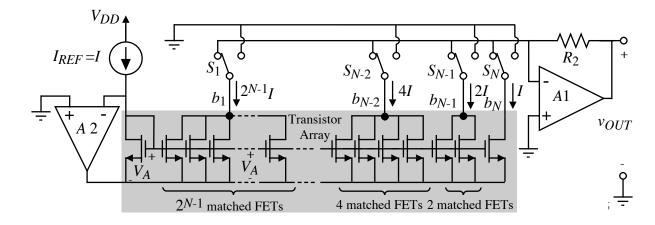

#### Current Scaling D/As

The output voltage can be expressed as

$$V_{out} = R_f(I_1 + I_2 + I_3 + \dots + I_N)$$

where the currents *I*1, *I*2, *I*3, ... are binary weighted currents.

Fast (no moving nodes) and not monotonic (mismatch)

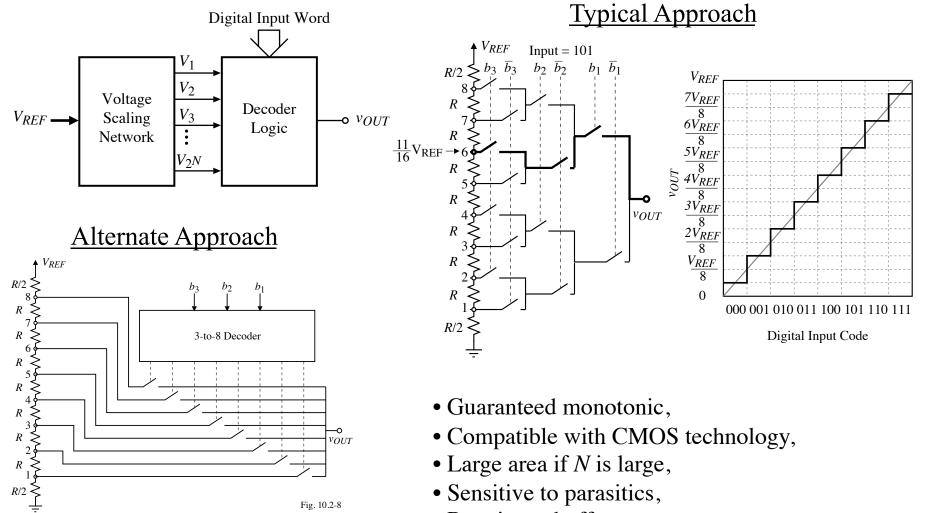

## Voltage Scaling D/As

- Requires a buffer,

- Large current can flow through the resistor string.

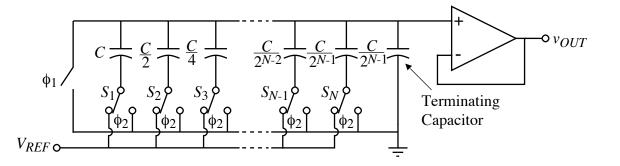

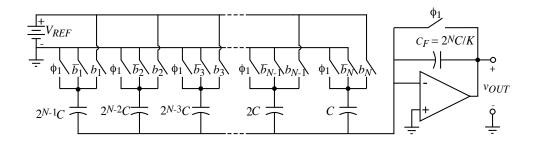

### Charge Based D/A Converters

Based on capacitor matching (not monotonic) Charge feedthrough and parasitic issues

- No moving nodes

- insensitive to parasitics

(parasitic-insensitive switched capacitor circuitry)

- fast

Can not eliminate charge feedthrough

## Improving D/A Performance

Divide the total resolution N into k smaller sub-DACs.

- Smaller total area.

- More resolution (reduced largest to smallest component spread)

So how do we do this?

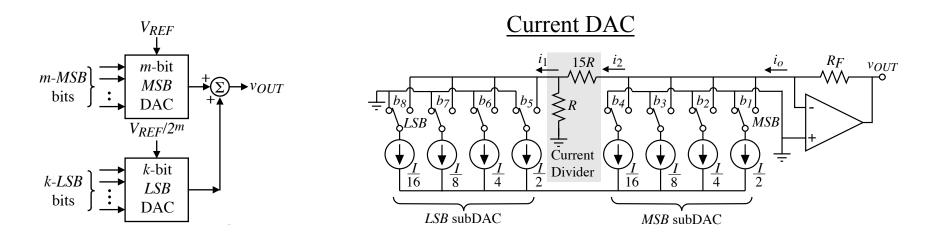

- Combination of similarly scaled subDACs

Divider approach (scale the analog output of the subDACs)

Subranging approach (scale the reference voltage of the subDACs)

- Combination of differently scaled subDACs

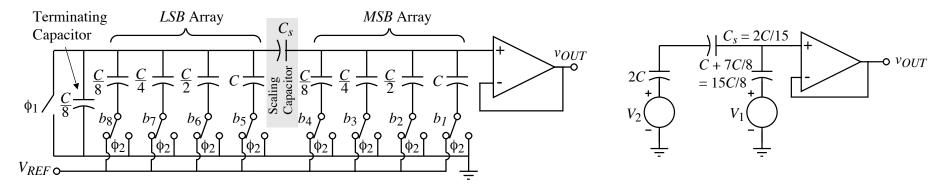

### Subranging Converters

Charge DAC

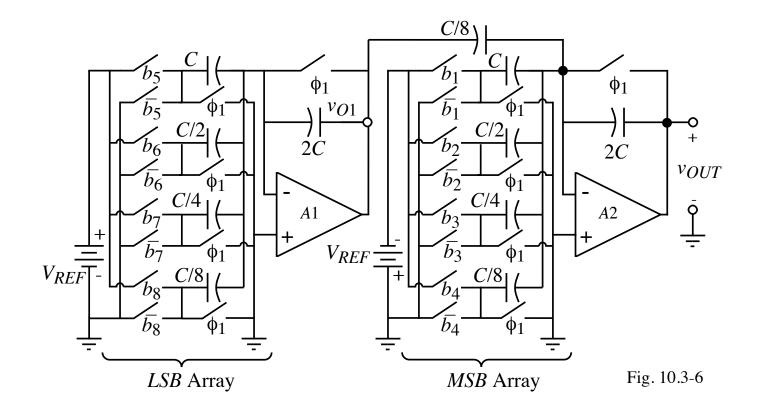

### D/A Based on Two Charge Amps

- *MSB* subDAC is not dependent upon the accuracy of the scaling factor for the *LSB* subDAC.

- Insensitive to parasitics, fast

- Limited to op amp dynamics

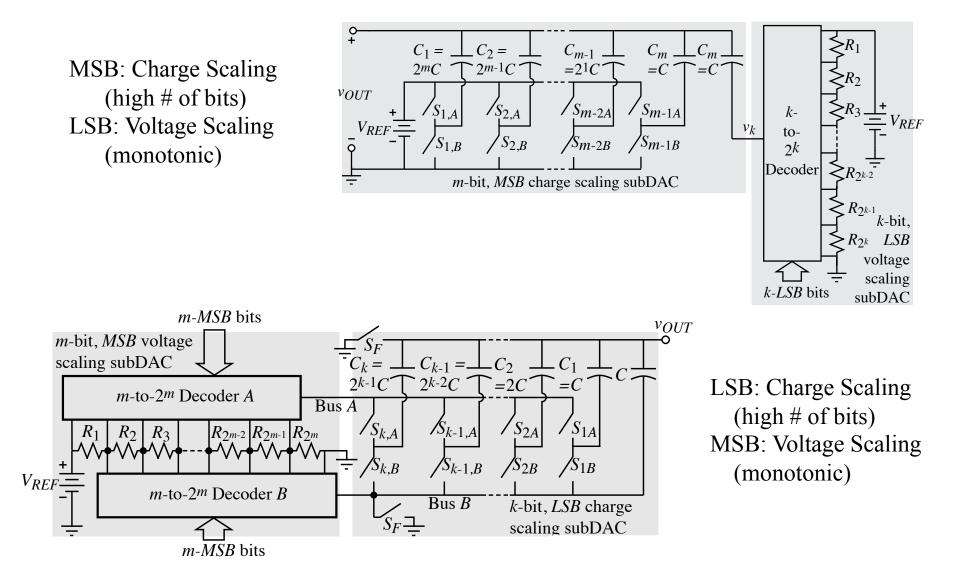

## Combining Unique SubDACs

# Summary of D/A Converters

| DAC                                                                | Figure  | Primary Advantage                                                    | Primary Disadvantage                                                                   |

|--------------------------------------------------------------------|---------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Current-scaling, binary weighted resistors                         | 10.2-3  | Fast, insensitive to parasitic capacitance                           | Large element spread, nonmonotonic                                                     |

| Current-scaling, R-2R<br>ladder                                    | 10.2-4  | Small element spread, increased accuracy                             | Nonmonotonic, limited to resistor accuracy                                             |

| Current-scaling, active devices                                    | 10.2-5  | Fast, insensitive to switch parasitics                               | Large element spread, large area                                                       |

| Voltage-scaling                                                    | 10.2-7  | Monotonic, equal resistors                                           | Large area, sensitive to parasitic capacitance                                         |

| Charge-scaling,<br>binary weighted capacitors                      | 10.2-10 | Best accuracy                                                        | Large area, sensitive to parasitic capacitance                                         |

| Binary weighted, charge amplifier                                  | 10.2-12 | Best accuracy, fast                                                  | Large element spread, large area                                                       |

| Current-scaling subDACs using current division                     | 10.3-3  | Minimizes area, reduces element spread which enhances accuracy       | Sensitive to parasitic capacitance, divider must have $\pm 0.5LSB$ accuracy            |

| Charge-scaling subDACs using charge division                       | 10.3-4  | Minimizes area, reduces element spread which enhances accuracy       | Sensitive to parasitic capacitance, slower,<br>divider must have $\pm 0.5LSB$ accuracy |

| Binary weighted charge amplifier subDACs                           | 10.3-6  | Fast, minimizes area, reduces element spread which enhances accuracy | Requires more op amps, divider must have $\pm 0.5LSB$ accuracy                         |

| Voltage-scaling ( <i>MSBs</i> ),<br>charge-scaling ( <i>LSBs</i> ) | 10.3-7  | Monotonic in <i>MSBs</i> , minimum area, reduced element spread      | Must trim or calibrate resistors for absolute accuracy                                 |

| Charge-scaling ( <i>MSBs</i> ), voltage-scaling ( <i>LSBs</i> )    | 10.3-8  | Monotonic in <i>LSBs</i> , minimum area, reduced element spread      | Must trim or calibrate resistors for absolute accuracy                                 |

| Serial, charge redistribution                                      | 10.4-1  | Simple, minimum area                                                 | Slow, requires complex external circuits                                               |

| Pipeline, algorithmic                                              | 10.4-3  | Repeated blocks, output at each clock after <i>N</i> clocks          | Large area for large number of bits                                                    |

| Serial, iterative algorithmic                                      | 10.4-4  | Simple, one precise set of components                                | Slow, requires additional logic circuitry                                              |