### Acquisition and Hold Time

#### Acquisition Time

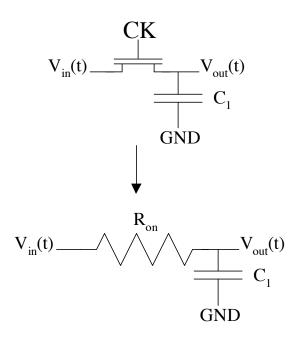

but R<sub>on</sub> is not a constant....

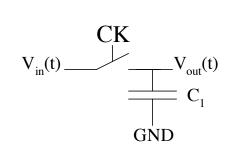

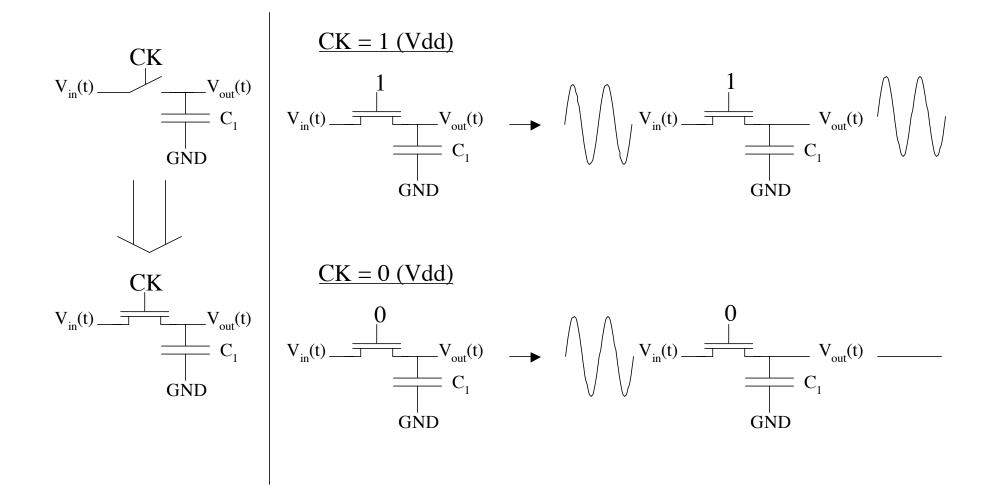

# $\underbrace{\frac{\text{Hold Time}}{0}}_{V_{in}(t)} \underbrace{\frac{0}{1}}_{I_1} \underbrace{V_{out}(t)}_{I_2} \underbrace{\frac{1}{1}}_{I_2} \underbrace$

- I<sub>2</sub>(t): Leakage through the reversed-biased pn junction Typically 1fA to 100fA (dark)

- I<sub>1</sub>(t): Leakage through the MOS transistor Can be negligable with correct biasing

| <u>C</u> <sub>1</sub> | Hold time (1mV drop) with $I_{\underline{1}}(t) = 10fA$ |

|-----------------------|---------------------------------------------------------|

| 10pF                  | 1s                                                      |

| 1pF                   | 100ms                                                   |

| 100fF                 | 10ms                                                    |

| 10fF                  | 1ms                                                     |

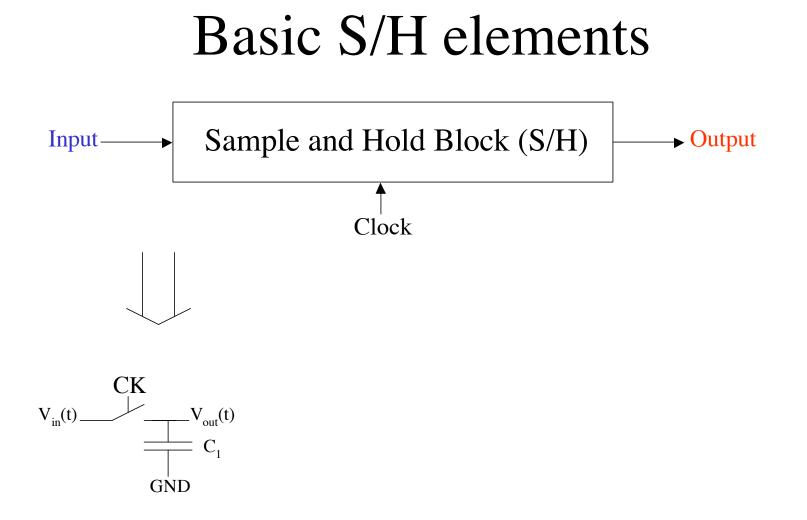

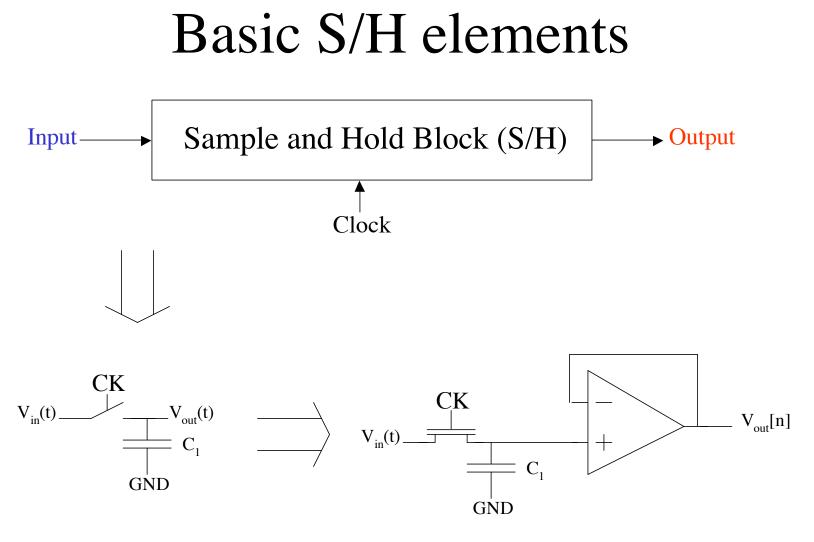

Would use a buffer to drive loads that are not purely capacitive

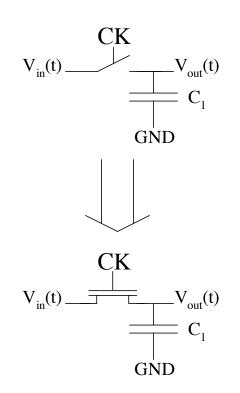

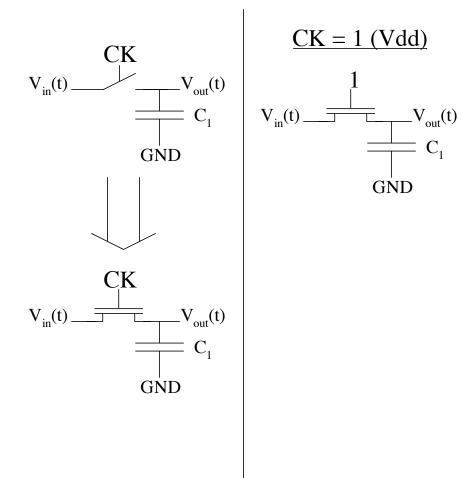

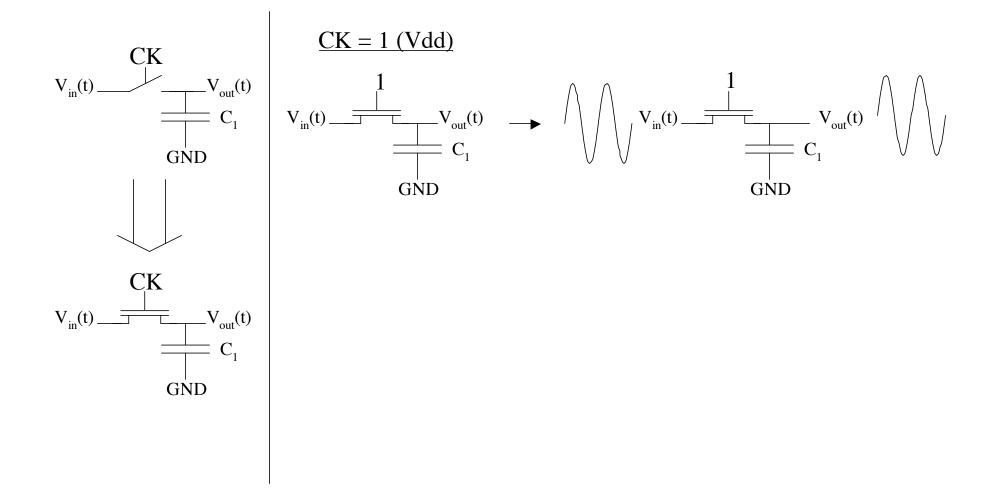

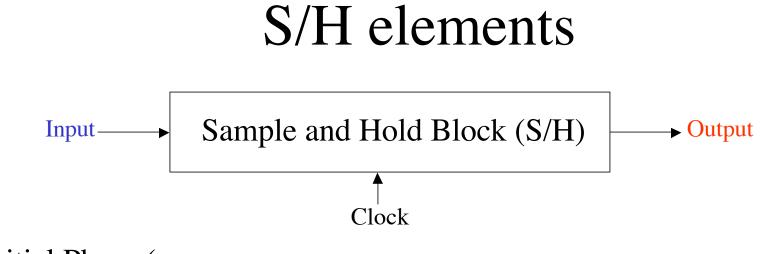

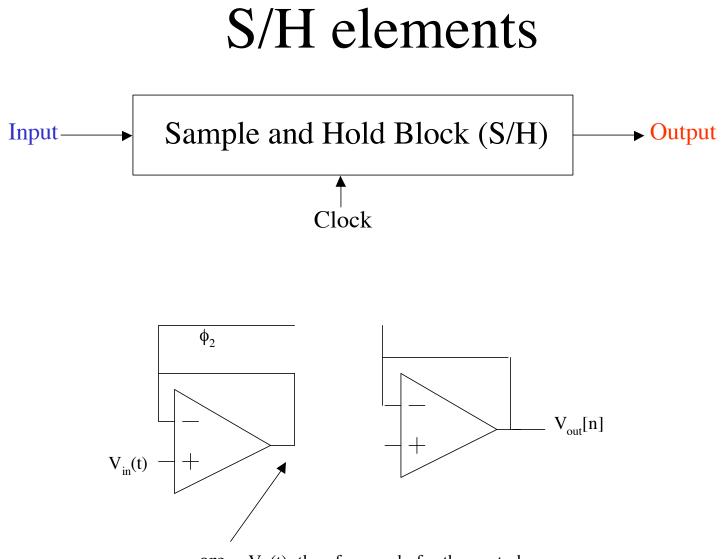

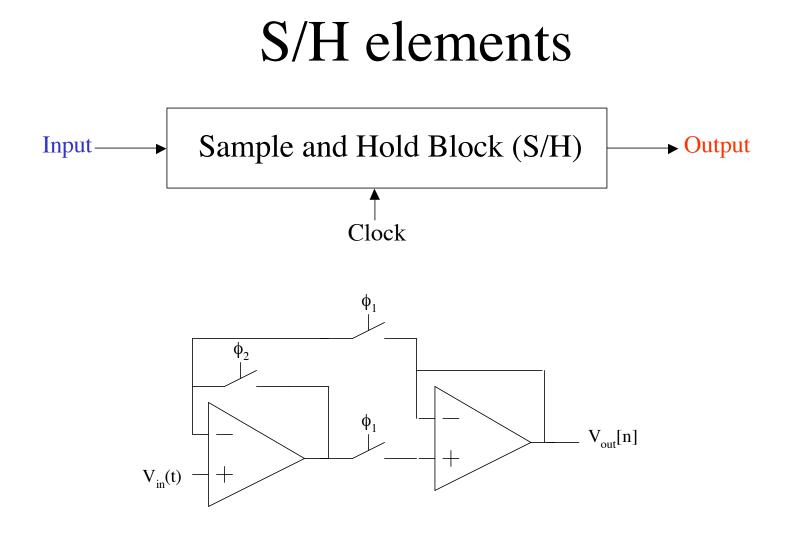

# Non-Overlapping Clocks

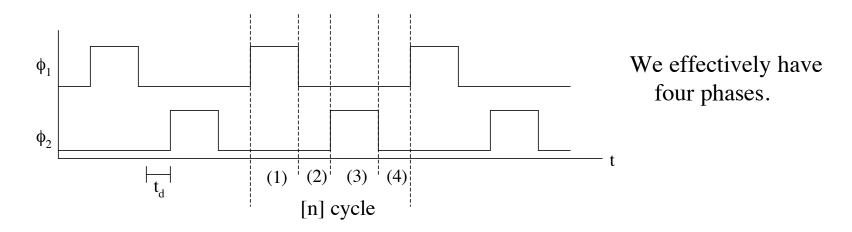

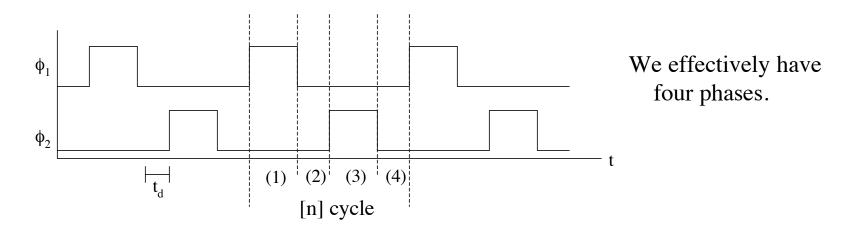

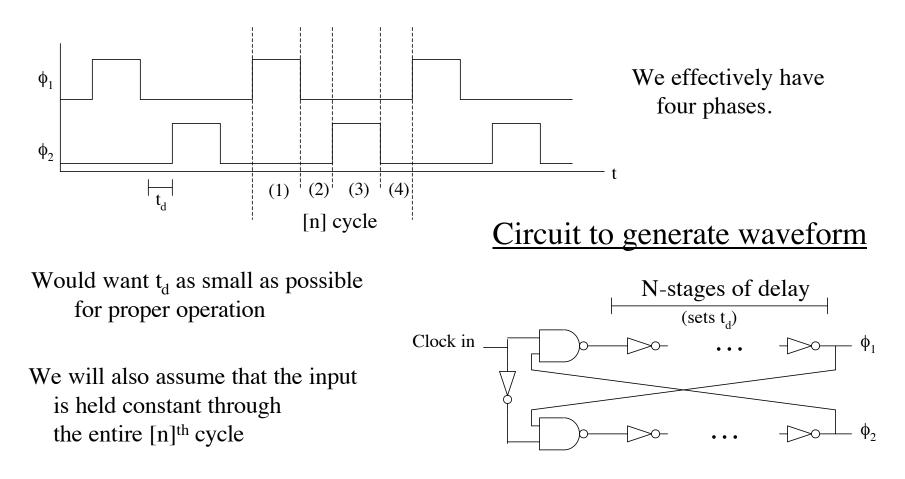

We will always be using non-overlapping clocks; therefore, we want a waveform like

# Non-Overlapping Clocks

We will always be using non-overlapping clocks; therefore, we want a waveform like

Would want t<sub>d</sub> as small as possible for proper operation

We will also assume that the input is held constant through the entire [n]<sup>th</sup> cycle

# Non-Overlapping Clocks

We will always be using non-overlapping clocks; therefore, we want a waveform like

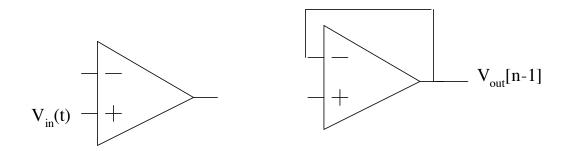

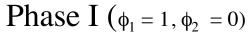

Initial Phase  $(\phi_1, \phi_2 = 0)$

Phase II ( $\phi_1, \phi_2 = 0$ )

are  $\sim V_{in}(t)$ ; therefore ready for the next phase

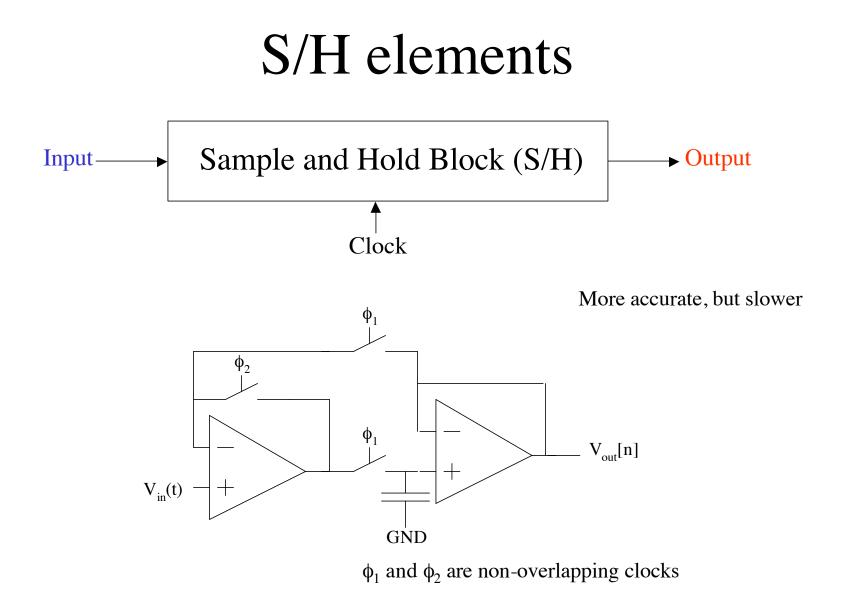

$\varphi_1$  and  $\varphi_2$  are non-overlapping clocks