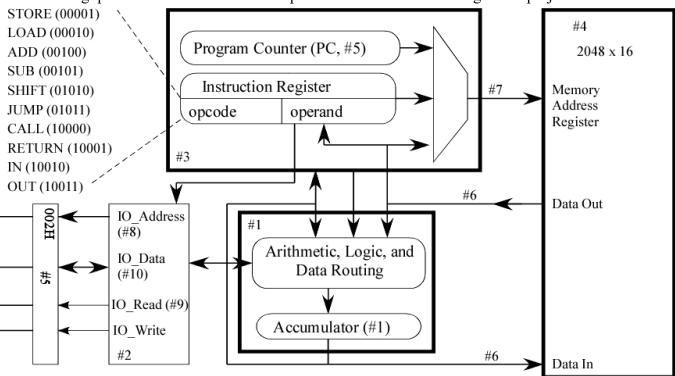

Question #1-#4 are matching with the following components

Question #6-10 are digital bus sizes (widths)

| components |    |                |     |       |

|------------|----|----------------|-----|-------|

|            |    | a. Memory      |     | a. 1  |

|            | 1. | b. Interrupt   | 6.  | b. 2  |

|            | _  | c. ALU         |     | c. 4  |

|            | 2. | d. Timer       | 7.  | d. 5  |

|            | _  | e. Peripheral  | •   | e. 11 |

|            | 3. | f. Cache       | 8.  | f. 12 |

|            | _  | g. Control     |     | g. 15 |

|            | 4. | h. LED display | 9.  | h. 16 |

|            | _  |                |     |       |

|            | 5. |                | 10. |       |

| 11. What instruction           | 12. What command is             | 13. What command is           |

|--------------------------------|---------------------------------|-------------------------------|

| would you use to multiply a    | used to send the accumulator to | used to execute a subroutine? |

| number in the accumulator by 4 | an IO port?                     | a. RETURN                     |

| in a single instruction?       | a. JUMP                         | b. IN                         |

| a. ADD                         | b. IN                           | c. CALL                       |

| b. SUB                         | c. SHIFT                        | d. OUT                        |

| c. JUMP                        | d. OUT                          | e. JMP                        |

| d. SHIFT                       | e. LOAD                         |                               |

| e. LOAD                        |                                 |                               |

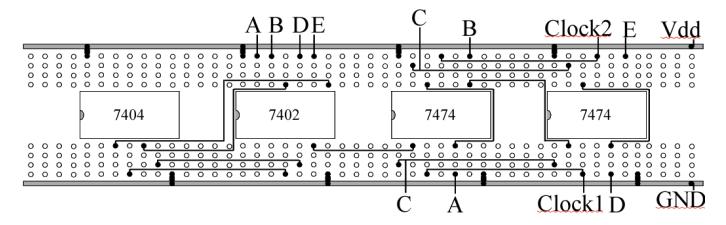

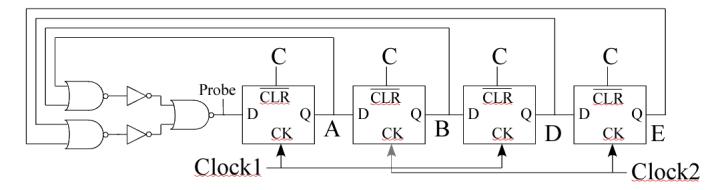

Your company has a critical component used in a larger system that was made from discrete parts that you want to have implemented as part of an FPGA. The problem has been assigned to you to take this component, analyze it, and make an FPGA implementation. The diagram from a breadboard, like the solderless breadboards you use in class is below. The design uses familiar 7402, 7404, and 7474 chips that you have used in lab where one should assume roughly 10ns delay for a gate through this breadboard.

The board has five signals, A, B, C, D, & E and two non-overlapping clock signals, Clock1 & Clock2.

Draw the gate level diagram for this circuit.

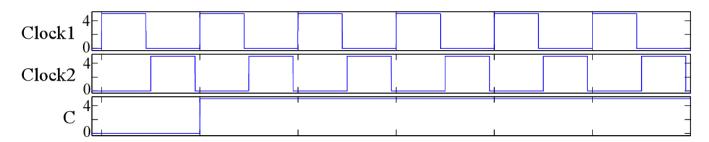

For this problem, continue the problem assuming the following solution (from first objective part), where we still have a gate delay of 10ns in the protoboard. Clock1, Clock2 are the clock inputs, and C is also an input into the circuit.

What is the logic function between A, B, D, and E and the Probe output? What is the propagation delay?

Complete the timing diagram for the remaining signals and the probe signal. Why are the clocks non-overlapping and alternating for the four shift registers? Describe the output you would see if C = 0? What does the C signal do?

| What is the VHDL code for your implementation that performs the same function as this circuit? |

|------------------------------------------------------------------------------------------------|

|                                                                                                |

|                                                                                                |

|                                                                                                |

|                                                                                                |

|                                                                                                |

|                                                                                                |

|                                                                                                |

|                                                                                                |

|                                                                                                |

|                                                                                                |

|                                                                                                |

|                                                                                                |

|                                                                                                |

|                                                                                                |