# **CHARGE-BASED ANALOG CIRCUITS FOR**

# **RECONFIGURABLE SMART SENSORY SYSTEMS**

A Dissertation Presented to The Academic Faculty

By

Sheng-Yu Peng

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology August 2008

Copyright © 2008 by Sheng-Yu Peng

# CHARGE-BASED ANALOG CIRCUITS FOR RECONFIGURABLE SMART SENSORY SYSTEMS

Approved by:

Dr. Paul E. Hasler, Advisor Professor, School of ECE Georgia Institute of Technology Atlanta, GA

Dr. David V. Anderson Professor, School of ECE Georgia Institute of Technology Atlanta, GA

Dr. F. L. Degertekin Professor, School of ECE Georgia Institute of Technology Atlanta, GA Dr. Maysam Ghovanloo Professor, School of ECE Georgia Institute of Technology Atlanta, GA

Dr. Bradley A. Minch Professor, Department of ECE Franklin W. Olin College of Engineering Needham, MA

Date Approved: June 2008

# **DEDICATION**

To my loving family ...

#### ACKNOWLEDGMENTS

I would like to express my sincere gratitude to everyone who has supported and helped me during my long journey of pursuing Ph.D. degree. Without them, I would not have made it this far.

First of all, I would like to thank my advisor, Dr. Paul Hasler, for giving me all the opportunities at Georgia Tech in all aspects along with his invaluable guidance, constant support, and persistent encouragement, which make this research and dissertation possible. I am especially grateful for his kindness and amicability. To me, he is not only an advisor during my academic years but also as a friend in my life as well as on the basketball court.

I would also like to thank Dr. Bradley Minch for his inspiring lectures and unreserved sharing that bring me into the field of analog signal processing. I am also thankful for his consistent advice and help since the beginning of my journey.

I would also like to extend my appreciation to Dr. David Anderson and Dr. F. L. Degertekin for the insightful comments on my research and all the advice on my academic studies and help in my career planning. I would like to thank Dr. Jennifer Michaels for serving on my dissertation proposal committee, and Dr. Maysam Ghovanloo for serving on my dissertation defense committee.

I would like to say thank you to Kofi Odame and Walter Huang for their help, patience, and companionship. Many thanks to members of CADSP research group for helping and teaching me lots of knowledge and skills that I would never have learned from class. I am very thankful to Ethan, Christal, David, Erhan, Gail, Venkatesh, Christopher, Guillermo, Venkatesh, David, Ryan, Degs, Huseyin, and Arindam, Shakeel, Gokce, Chris, Jordan, Scott, Shubha, Craig, Richie, Stephen, Csaba, Michael, Sourabh, and Shyam for their friendship and support. I will also like to thank collaboration partners working in the Love Building. I benefit a lot from working with Dr. Mustafa Karaman, Dr. Mujdat Balantekin, Dr. Rasim Guldiken and Jaime Zahorian. I would also like to thank Yu Tsao for his help in this research. He and lots of friends in TSA make my stay at Atlanta a memorable and enjoyable experience.

Special thanks go to Fanpei Yang for her listening, encouragement, and love, which have brought me the strength to strive through all the harsh times without feeling alone during my graduate life. Finally, I am deeply indebted to my parents and my brother for all the sacrifices they have made for me to succeed throughout my life and for their unconditional support and endless love.

# TABLE OF CONTENTS

| ACKNO   | WLEDGMENTS                                            | iv  |

|---------|-------------------------------------------------------|-----|

| LIST OF | TABLES                                                | ix  |

| LIST OF | FIGURES                                               | Х   |

| SUMMA   | RY                                                    | XV  |

| CHAPTI  | ER 1 RECONFIGURABLE SMART SENSORY SYSTEM              | 1   |

| 1.1     | Advanced Sensory Microsystems                         | 1   |

| 1.2     | Analog Signal Processing                              |     |

| 1.3     | Charge-Based Analog Design                            | 3   |

| 1.4     | Reconfigurable Smart Sensory Chip                     | 4   |

| CHAPTI  | ER 2 PROGRAMMABLE ANALOG TECHNOLOGIES                 | 6   |

| 2.1     | Capacitive Circuits                                   | 6   |

| 2.2     | Floating-Gate Transistor                              | 9   |

| 2.3     | Floating-Gate Programming                             | 10  |

| CHAPTI  | ER 3 A CHARGE-BASED LOW-POWER CAPACITIVE SENSING IN   | -   |

|         | TERFACE CIRCUIT                                       | 17  |

| 3.1     | Challenges in Capacitive Sensing                      | 17  |

| 3.2     | Capacitive Sensing Charge Amplifier                   | 18  |

|         | 3.2.1 Transfer function                               | 19  |

|         | 3.2.2 Noise analysis                                  | 21  |

|         | 3.2.3 Maximum dynamic range                           | 22  |

|         | 3.2.4 Signal-to-noise ratio                           | 24  |

|         | 3.2.5 Measurement results                             | 25  |

| 3.3     | Floating-Gate-Based Charge Adaptation                 |     |

|         | 3.3.1 Audio applications                              |     |

|         | 3.3.2 Ultrasonic applications                         |     |

| 3.4     | Design Procedure                                      | 34  |

| 3.5     | Comparison                                            |     |

| 3.6     | Conclusion                                            | 37  |

| CHAPTI  | ER 4 CAPACITIVE SENSING FOR MICROMACHINED ULTRASON    | ۹IC |

|         | TRANSDUCER                                            | 40  |

| 4.1     | CMUTs for Intravascular Ultrasound Imaging            | 40  |

| 4.2     | Capacitive Sensing for CMUTs                          | 41  |

| 4.3     | The Charge Amplifier vs. The Transimpedance Amplifier | 43  |

| 4.4     | Pulse-Echo Measurement                                | 44  |

| 4.5     | Discussion                                            | 47  |

| CHAPTI | ER 5 RECONFIGURABLE ANALOG SIGNAL PROCESSOR WITH                |

|--------|-----------------------------------------------------------------|

|        | UNIVERSAL SENSOR INTERFACE                                      |

| 5.1    | Floating-Gate Based FPAA                                        |

| 5.2    | RASP 2.8 Design Overview49                                      |

| 5.3    | FPAA With Universal Sensor Interface    52                      |

| CHAPTI | ER 6 ANALOG IMPLEMENTATION OF RADIAL BASIS FUNCTIONS 57         |

| 6.1    | Conventional Bump circuit                                       |

| 6.2    | Previous Works on Floating-Gate Bump Circuits                   |

| 6.3    | Improved Programmable Floating-gate Bump circuit 61             |

| 6.4    | Multivariate Analog RBF Implementation                          |

| 6.5    | Conclusion                                                      |

| CHAPTI | ER 7 A PROGRAMMABLE ANALOG RBF-BASED CLASSIFIER . 71            |

| 7.1    | Information Refinement in The Analog Domain                     |

| 7.2    | Analog Classifiers                                              |

| 7.3    | The Architecture of The Analog Vector Quantizer                 |

| 7.4    | A Prototype Analog Vector Quantizer                             |

|        | 7.4.1 Power consumption                                         |

|        | 7.4.2 Bandwidth                                                 |

|        | 7.4.3 Performance                                               |

|        | 7.4.4 Power efficiency                                          |

| 7.5    | A $16 \times 16$ Analog Vector Quantizer                        |

|        | 7.5.1 Programming accuracy                                      |

|        | 7.5.2 Performance                                               |

|        | 7.5.3 Automated gender identification                           |

|        | 7.5.4 Power efficiency                                          |

| 7.6    | Conclusion                                                      |

| CHAPTI | ER 8 ADAPTIVE BUMP CIRCUIT FOR CLUSTERING 91                    |

| 8.1    | Dynamics of Two Source-Coupled pFET Synapses                    |

| 8.2    | Center-Adaptive Bump Circuits                                   |

| 8.3    | Center-and-Width Adaptive Bump Circuit                          |

| 8.4    | Adaptive Vector Quantizer for Clustering                        |

| CHAPTI | ER 9 ANALOG SUPPORT VECTOR MACHINE                              |

| 9.1    | Analog for Programming Problems                                 |

| 9.2    | Support Vector Machine For Classification                       |

| 9.3    | Projection Neural Network for SVM Learning                      |

|        | 9.3.1 Relevant theorems                                         |

|        | 9.3.2 The projection neural network for SVM                     |

| 9.4    | Analog Implementation of The Support Vector Classification 108  |

| 9.5    | Simulation Results                                              |

| 9.6    | The Projection Neural Network for Support Vector Regression 113 |

| 9.7 Conclusion            | • | <br>• |  | • | • |     | • |       | • | <br>• | • | <br>• | • | • | <br>• | 115 |

|---------------------------|---|-------|--|---|---|-----|---|-------|---|-------|---|-------|---|---|-------|-----|

| CHAPTER 10 CONCLUSION     | N |       |  |   |   |     |   |       |   |       |   |       |   |   |       | 117 |

| 10.1 Main Contributions . |   |       |  |   |   |     |   |       |   |       |   |       |   |   |       | 117 |

| 10.2 Research Summary .   |   |       |  |   | • | ••• | • | <br>• | • |       | • |       | • | • | <br>• | 117 |

| REFERENCES                |   |       |  |   |   |     |   |       |   |       |   |       |   | • |       | 120 |

# LIST OF TABLES

| Table 3.1 | Parameters and Measurement Results From A Capacitive Sensing Charge Amplifier |    |

|-----------|-------------------------------------------------------------------------------|----|

| Table 3.2 | CMUT Measurement Parameters                                                   | 34 |

| Table 3.3 | Performance Comparison                                                        | 38 |

| Table 7.1 | Analog Vector Quantizer Parameters and Performance                            | 77 |

| Table 7.2 | AGI Results                                                                   | 89 |

# LIST OF FIGURES

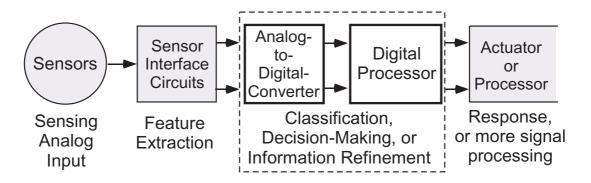

| Figure 1.1  | The block diagram of a typical sensory system                                                             | 1  |

|-------------|-----------------------------------------------------------------------------------------------------------|----|

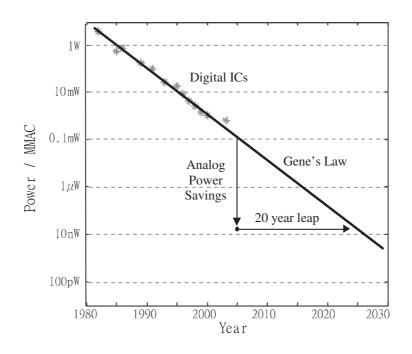

| Figure 1.2  | Power efficiency comparisons between analog and digital signal pro-<br>cessing                            | 3  |

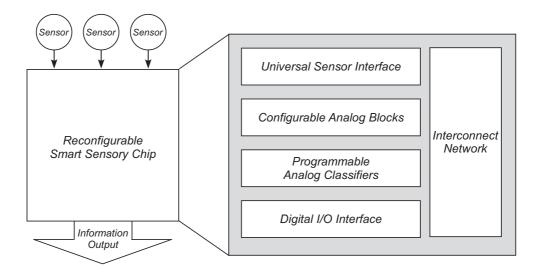

| Figure 1.3  | The block diagram of a reconfigurable smart sensory chip                                                  | 5  |

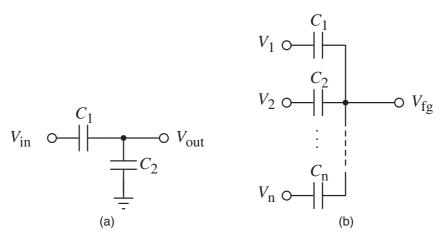

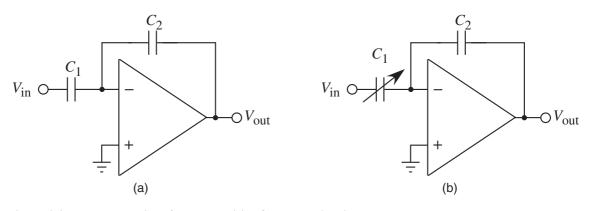

| Figure 2.1  | The schematics of two capacitive circuits.                                                                | 8  |

| Figure 2.2  | The schematics of capacitive feedback circuits                                                            | 9  |

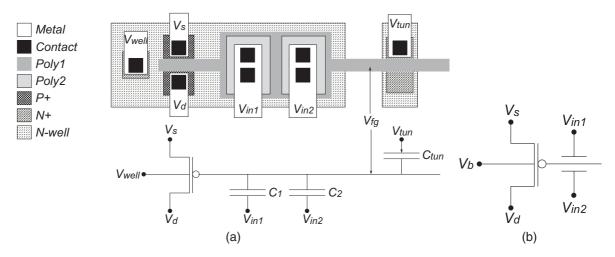

| Figure 2.3  | The circuit schematic, layout, and symbol of a pFET floating-gate transistor with two input capacitances. | 10 |

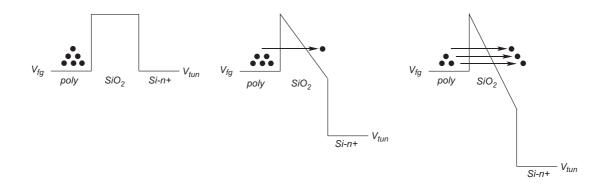

| Figure 2.4  | The conduction band diagram for tunneling process                                                         | 11 |

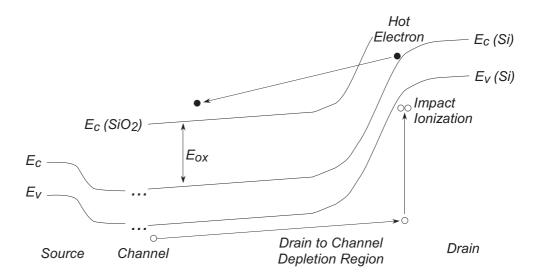

| Figure 2.5  | The band diagram for channel hot electron injection process                                               | 12 |

| Figure 2.6  | The time diagram of injection process.                                                                    | 13 |

| Figure 2.7  | The measured I-V curves after tunneling and injection                                                     | 13 |

| Figure 2.8  | Injection characterization.                                                                               | 14 |

| Figure 2.9  | Floating-gate array programming                                                                           | 15 |

| Figure 3.1  | The block diagram of a two-chip hybrid approach.                                                          | 17 |

| Figure 3.2  | The block diagram of the capacitive sensing                                                               | 18 |

| Figure 3.3  | The small-signal model of a capacitive sensing charge amplifier                                           | 19 |

| Figure 3.4  | The schematic of a single-stage cascode operational transconductance amplifier.                           | 19 |

| Figure 3.5  | Measured waveform from a capacitive sensing charge amplifier                                              | 21 |

| Figure 3.6  | The small-signal models of the capacitive sensing charge amplifier for noise analysis.                    | 22 |

| Figure 3.7  | Nonlinearity of an OTA                                                                                    | 23 |

| Figure 3.8  | The setup for audio measurements.                                                                         | 26 |

| Figure 3.9  | The micrographs of the charge amplifier and the MEMS sensor used in the measurement.                      | 27 |

| Figure 3.10 | The measured output signal and noise spectrums                                                            | 28 |

| Figure 3.11 | Noise spectrums of a charge amplifier with a linear input capacitor                                         | 28 |

|-------------|-------------------------------------------------------------------------------------------------------------|----|

| Figure 3.12 | Setup for the measurement with charge adaptation scheme                                                     | 30 |

| Figure 3.13 | The step responses of the capacitive sensing charge amplifier with a tunneling-injection adaptation scheme. | 31 |

| Figure 3.14 | The measured noise spectra with and without the adaptation circuit                                          | 31 |

| Figure 3.15 | Setup for the ultrasonic measurement.                                                                       | 33 |

| Figure 3.16 | Measured pulse-echo waveform from an ultrasonic transducer                                                  | 34 |

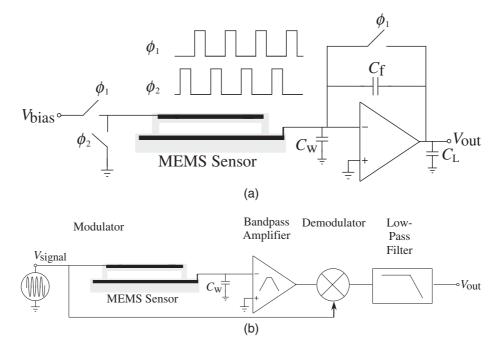

| Figure 3.17 | The block diagrams of the switched-capacitor and the lock-in approaches to capacitive sensing.              | 37 |

| Figure 3.18 | The block diagrams of the previous approaches to capacitive sensing for MEMS microphones.                   | 39 |

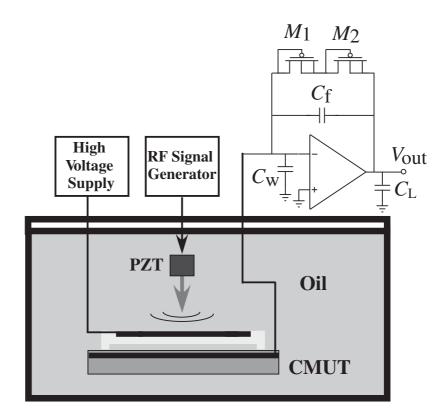

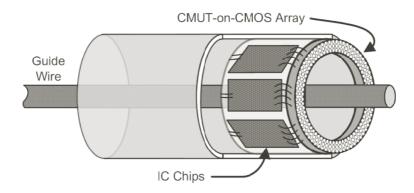

| Figure 4.1  | The block diagram of the IVUS catheter with integrated front-end electronics.                               | 41 |

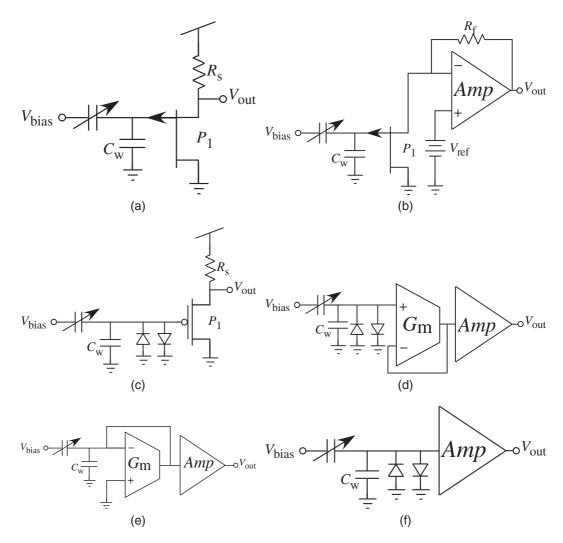

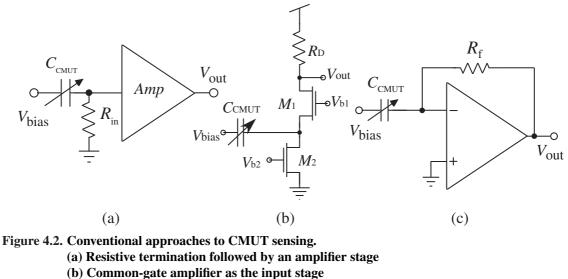

| Figure 4.2  | Conventional approaches to CMUT sensing.                                                                    | 42 |

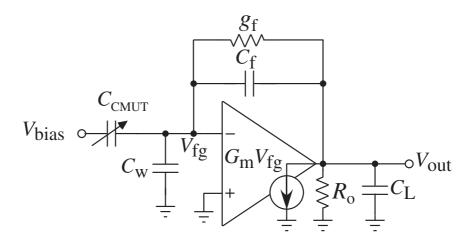

| Figure 4.3  | The small-signal model of a charge amplifier with charge adaptation feedback.                               | 43 |

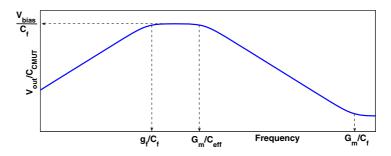

| Figure 4.4  | Simulated frequency response of the capacitive feedback charge amplifier with a feedback resistance.        | 44 |

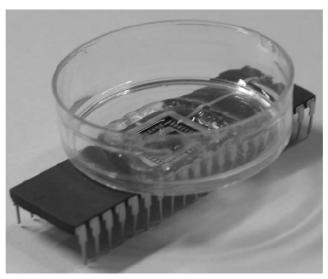

| Figure 4.5  | Photographs of the setup for the testing of CMUT sensing                                                    | 45 |

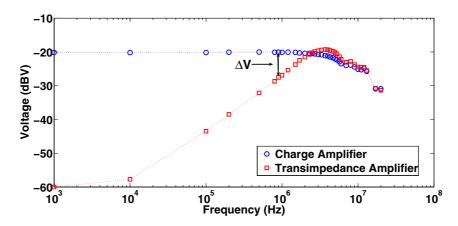

| Figure 4.6  | Comparison of the frequency response of a charge amplifier and a transimpedance amplifier.                  | 46 |

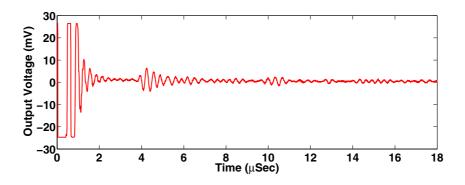

| Figure 4.7  | Measured pulse-echo response from a charge amplifier                                                        | 46 |

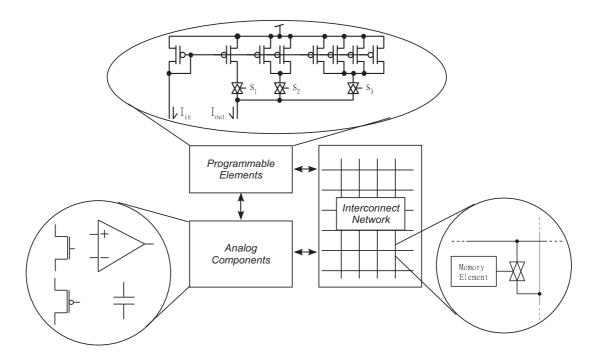

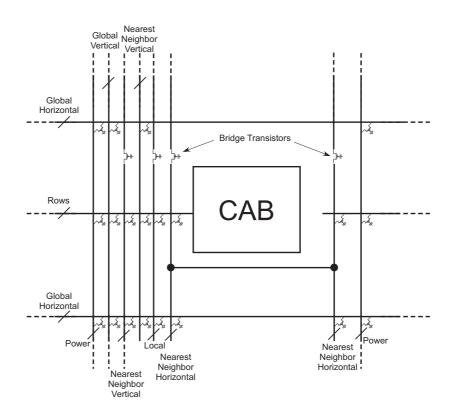

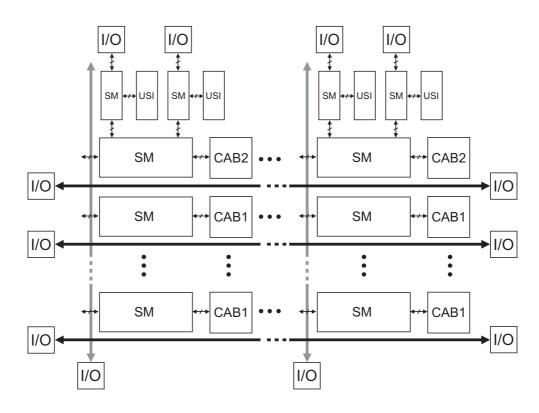

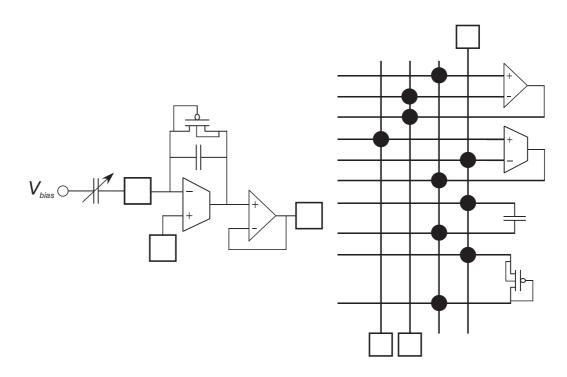

| Figure 5.1  | The architecture of a field programmable analog array                                                       | 49 |

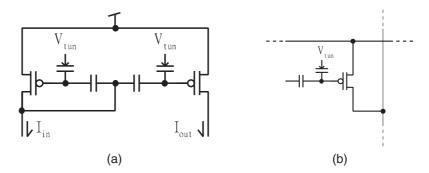

| Figure 5.2  | Floating-gate based programmable elements and switch for FPAA                                               | 49 |

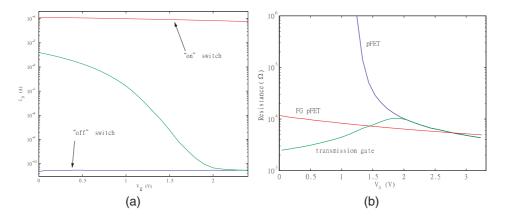

| Figure 5.3  | The characteristics of a floating-gate switch for FPAAs                                                     | 50 |

| Figure 5.4  | The block diagram of the RASP 2.8a                                                                          | 51 |

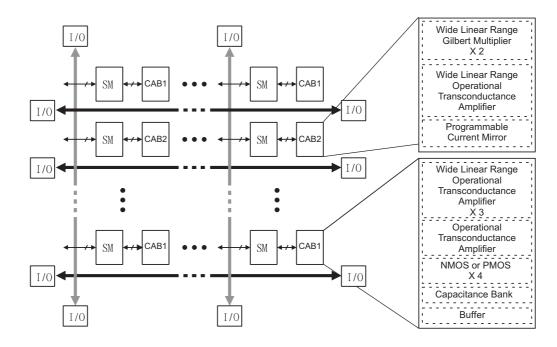

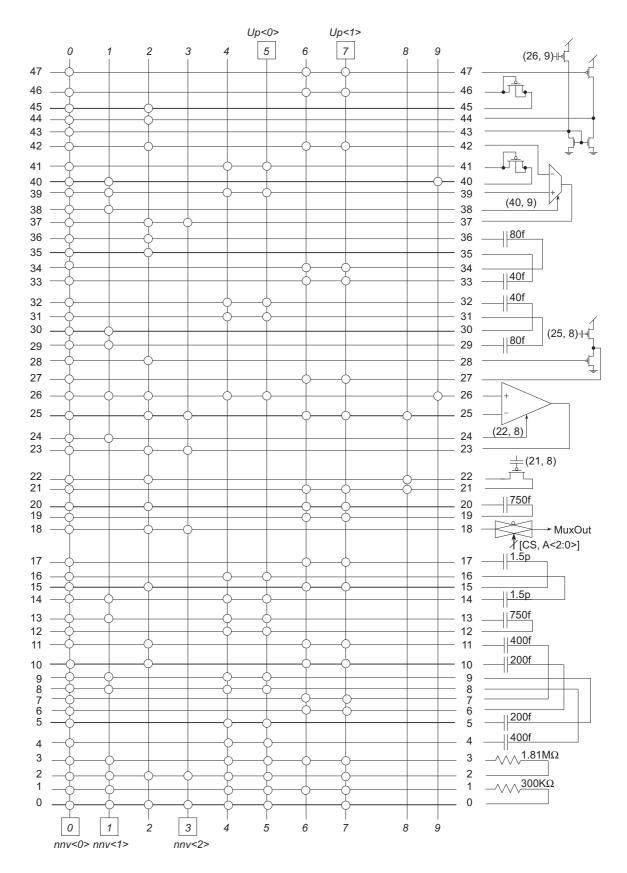

| Figure 5.5  | The architecture of routing in the RASP 2.8x series                                                         | 52 |

| Figure 5.6  | The architecture RASP2.8C                                                                                   | 53 |

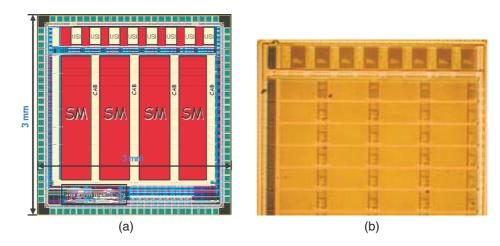

| Figure 5.7  | The layout and the micrograph of the RASP 2.8c.                                                             | 53 |

| Figure 5.8  | The fuse-network and components of a USI.                                             | 55 |

|-------------|---------------------------------------------------------------------------------------|----|

| Figure 5.9  | A capacitive sensing charge amplifier synthesized in the RASP 2.8c                    | 56 |

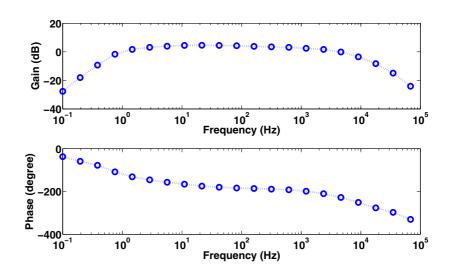

| Figure 5.10 | The frequency response measured from a charge amplifier synthesized in the RASP 2.8c. | 56 |

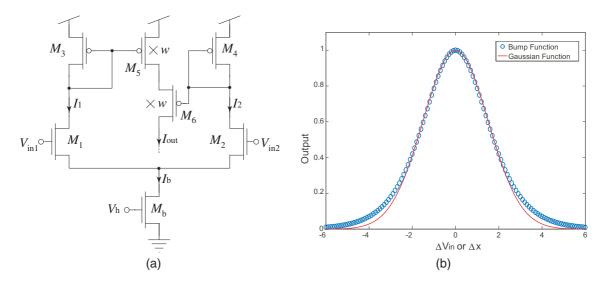

| Figure 6.1  | A simple bump circuit and its Gaussian-like DC transfer curve                         | 58 |

| Figure 6.2  | The schematic of a compact floating-gate bump circuit.                                | 60 |

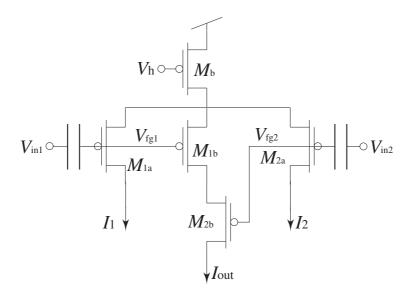

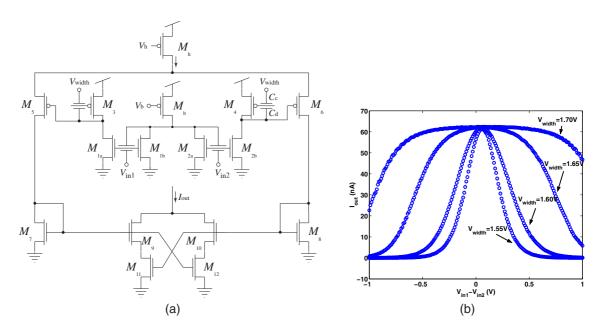

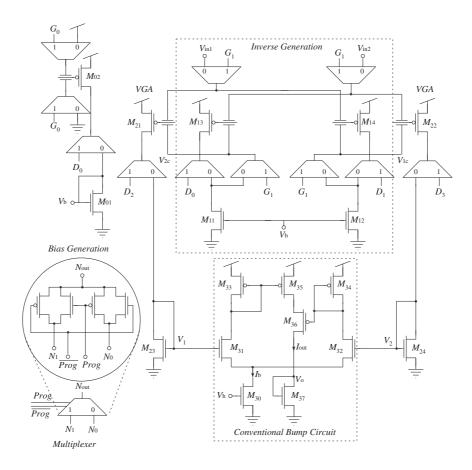

| Figure 6.3  | A proposed floating-gate bump circuit and the measured DC transfer curves.            | 61 |

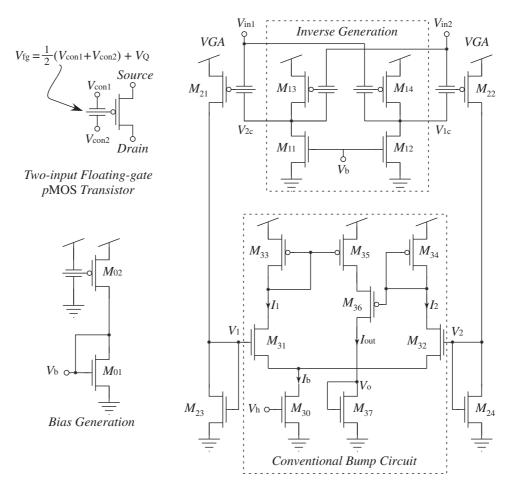

| Figure 6.4  | An improved version of the floating-gate bump circuit and its bias generation block.  | 62 |

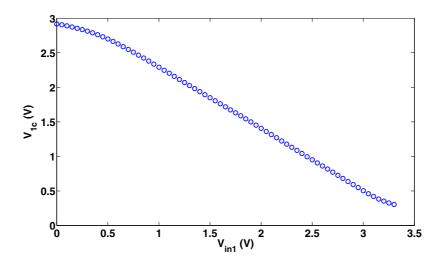

| Figure 6.5  | Transfer characteristics of the inverse generation block.                             | 63 |

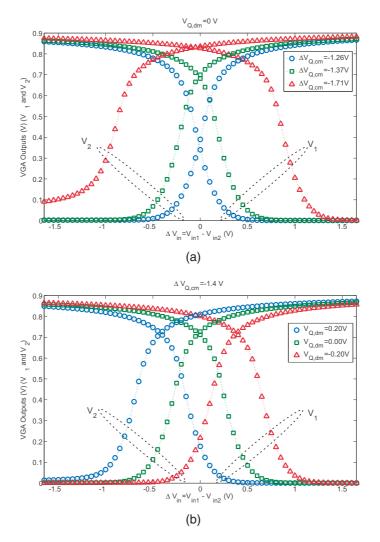

| Figure 6.6  | The transfer characteristics of the variable gain amplifier                           | 64 |

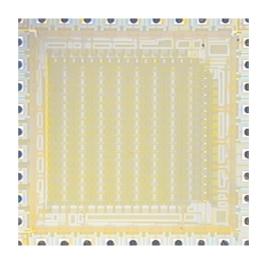

| Figure 6.7  | The micrograph of a prototype floating-gate bump circuit chip                         | 67 |

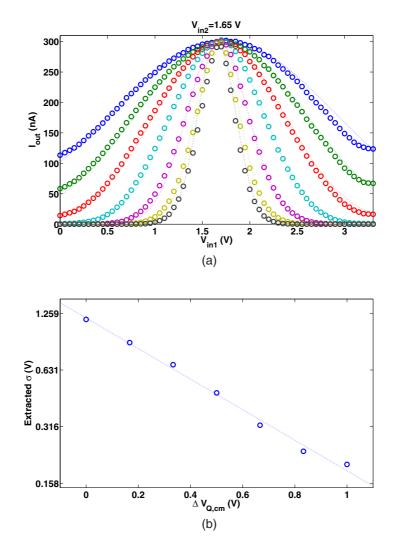

| Figure 6.8  | Gaussian fits of the transfer curves and the width dependance                         | 68 |

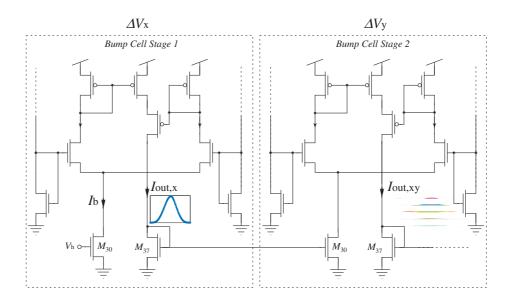

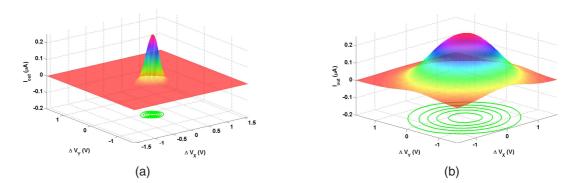

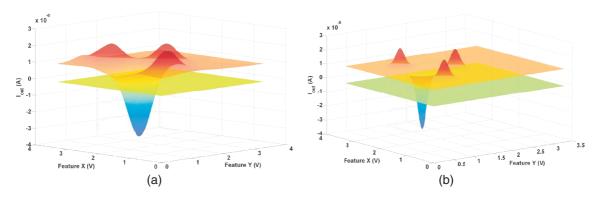

| Figure 6.9  | A bivariate radial basis function implementation.                                     | 69 |

| Figure 6.10 | Measured results of the bivariate radial basis function implementation.               | 69 |

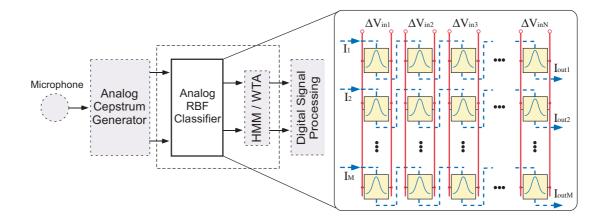

| Figure 7.1  | The block diagram of an analog system for speech recognition                          | 72 |

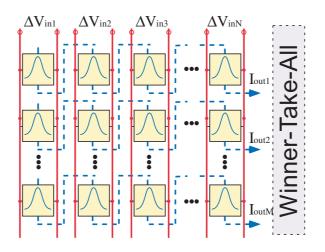

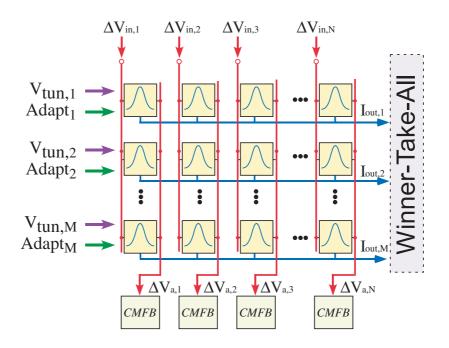

| Figure 7.2  | The block diagram of an analog RBF-based vector quantizer                             | 74 |

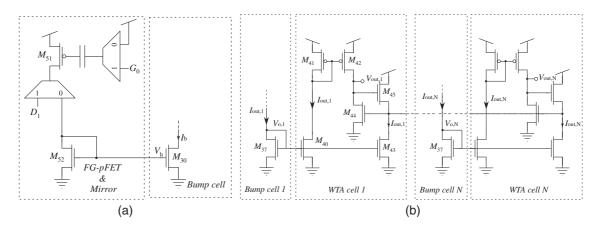

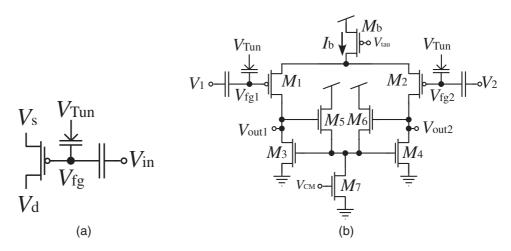

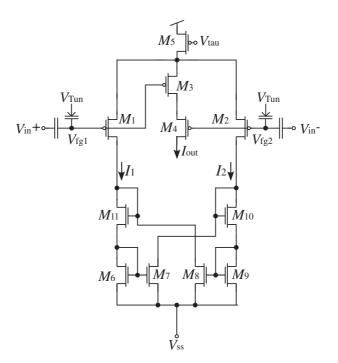

| Figure 7.3  | Complete schematics of the floating-gate bump circuit                                 | 75 |

| Figure 7.4  | The schematics of the "FG-pFET & Mirror" block and the winner-<br>take-all circuit.   | 76 |

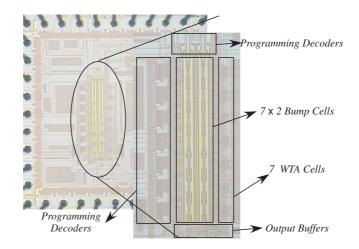

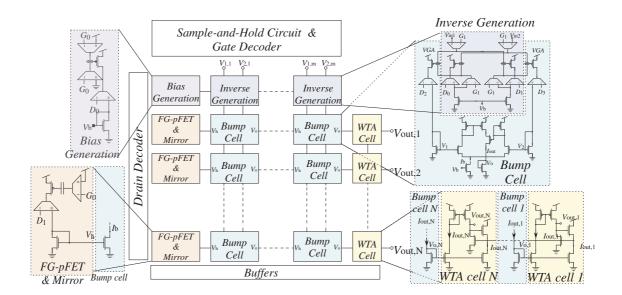

| Figure 7.5  | The architecture of an analog vector quantizer.                                       | 77 |

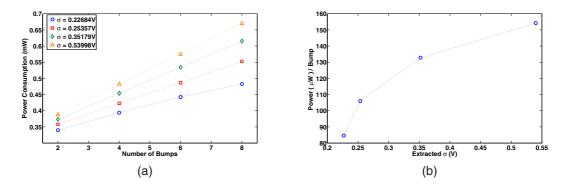

| Figure 7.6  | Configurable classification results.                                                  | 78 |

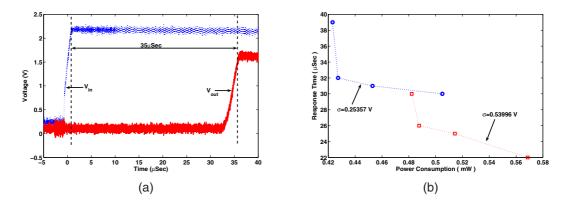

| Figure 7.7  | The relation between the power consumption and the extracted stan-<br>dard deviation. | 78 |

| Figure 7.8  | The transient response and the speed-power tradeoff                                   | 79 |

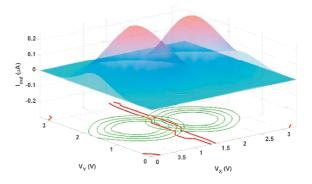

| Figure 7.9  | The distributions of two "bumps" used to evaluate the classifier per-<br>formance.    | 81 |

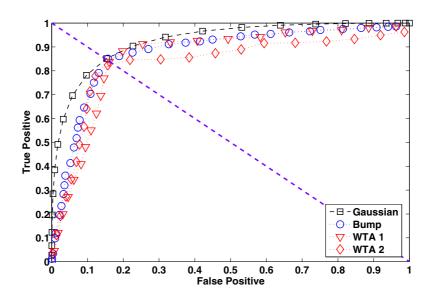

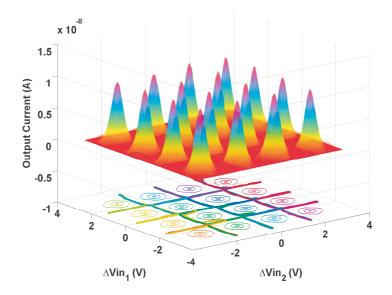

| Figure 7.10 | The ROC performance of the classifiers.                                               | 81 |

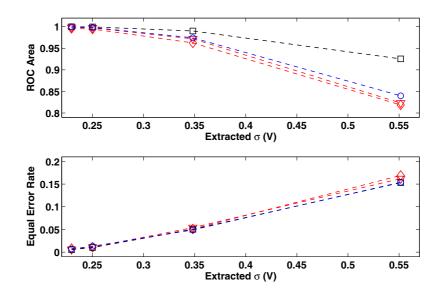

| Figure 7.11 | The effects of the bump widths on the ROC area and the EER perfor-<br>mance.                | 82  |

|-------------|---------------------------------------------------------------------------------------------|-----|

| Figure 7.12 | The micrograph of the $16 \times 16$ analog vector quantizer                                | 83  |

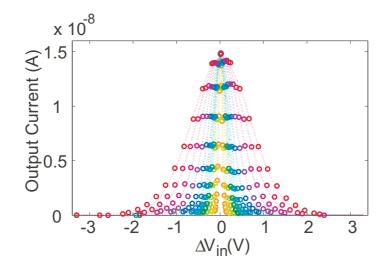

| Figure 7.13 | The transfer curves of a floating-gate bump circuit in the analog vector quantizer.         | 84  |

| Figure 7.14 | The common-mode charge and the extracted standard deviation in the analog vector quantizer. | 84  |

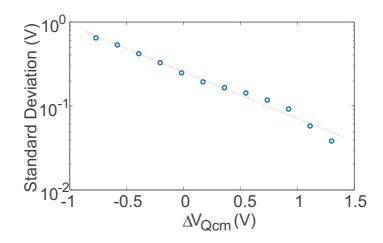

| Figure 7.15 | The transfer curves of 16 different floating-gate bump circuits in the same template.       | 85  |

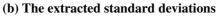

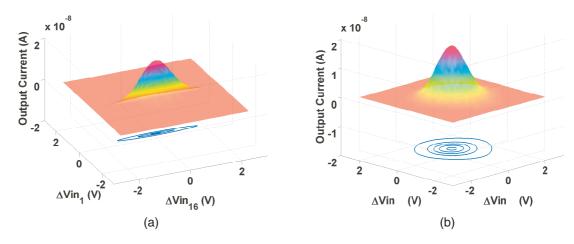

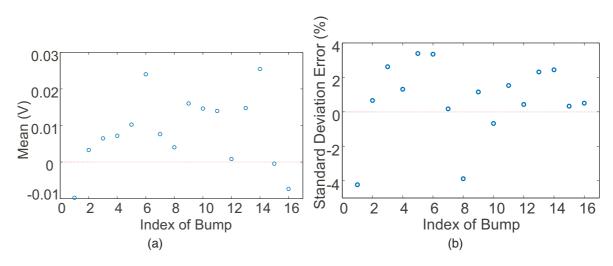

| Figure 7.16 | The programming accuracy of 16 different floating-gate bump circuits in the same template.  | 85  |

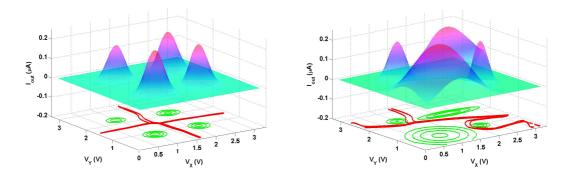

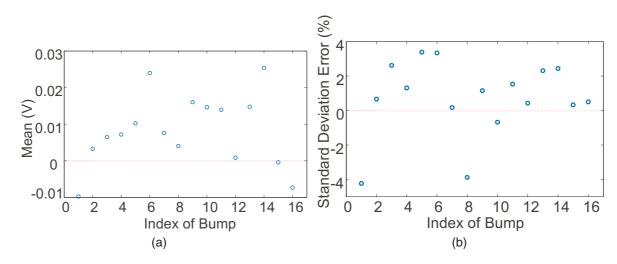

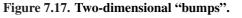

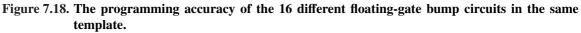

| Figure 7.17 | Two-dimensional "bumps".                                                                    | 86  |

| Figure 7.18 | The programming accuracy of 16 different floating-gate bump circuits in the same template.  | 86  |

| Figure 7.19 | The transfer curves of a floating-gate bump circuit in the analog vector quantizer.         | 87  |

| Figure 7.20 | The ROC curves measured from the $16 \times 16$ analog vector quantizer.                    | 87  |

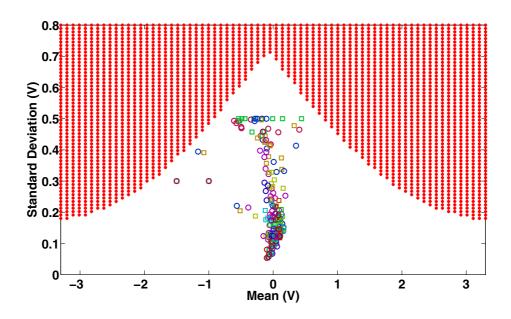

| Figure 7.21 | The effective region for programmable means and variances                                   | 89  |

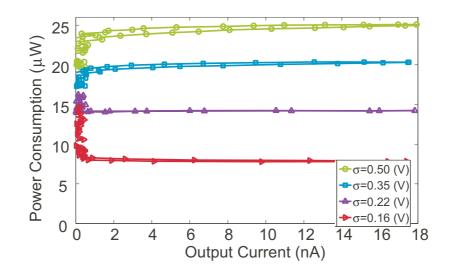

| Figure 7.22 | The power consumption of a bump cell with different widths                                  | 90  |

| Figure 8.1  | The schematics of a pFET synapse and two source-coupled pFET synapses.                      | 92  |

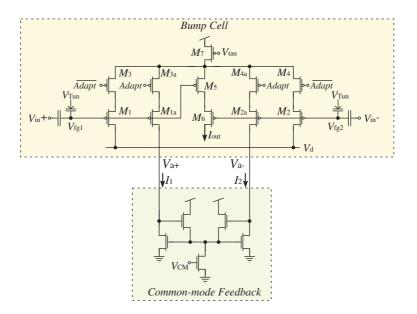

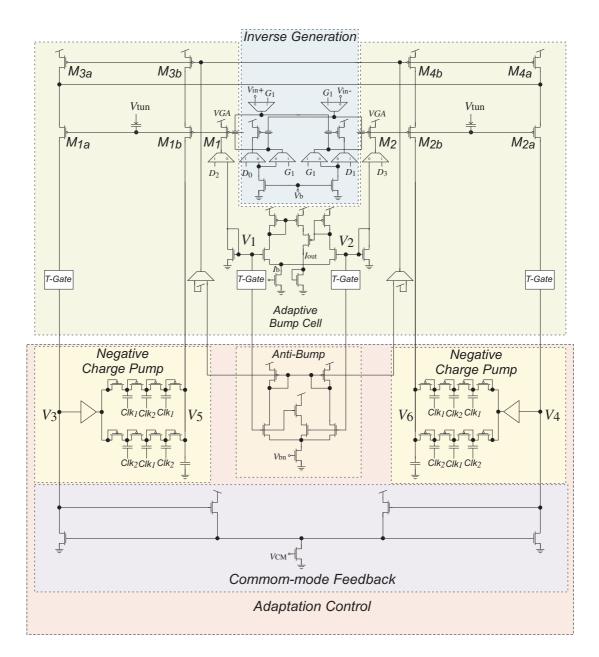

| Figure 8.2  | An adaptive floating-gate bump circuit.                                                     | 94  |

| Figure 8.3  | An center-adaptive vector quantizer.                                                        | 95  |

| Figure 8.4  | An Automaximizing bump circuit.                                                             | 96  |

| Figure 8.5  | A center-and-width adaptive bump circuit.                                                   | 97  |

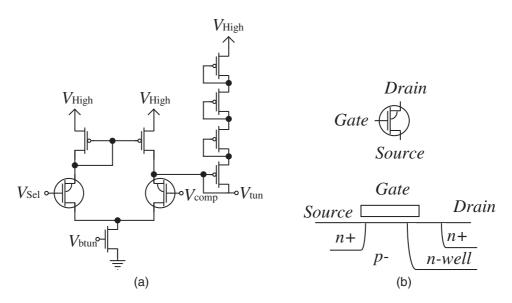

| Figure 8.6  | The schematics of a tunneling select circuit and the structure of a high-voltage nFET.      | 98  |

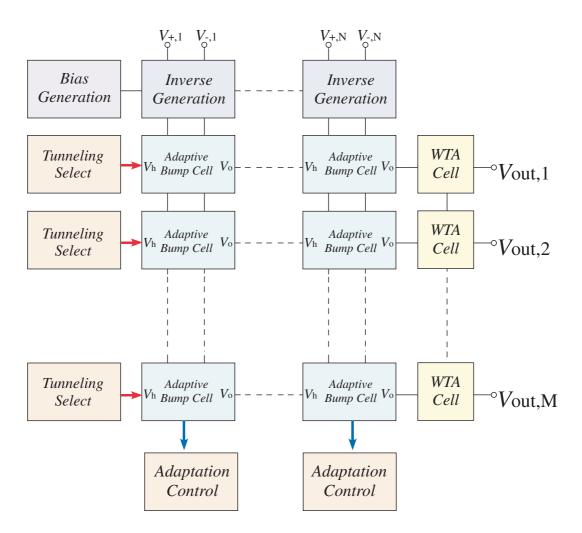

| Figure 8.7  | An adaptive vector quantizer.                                                               | 99  |

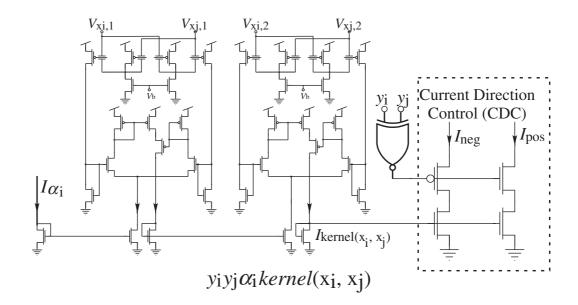

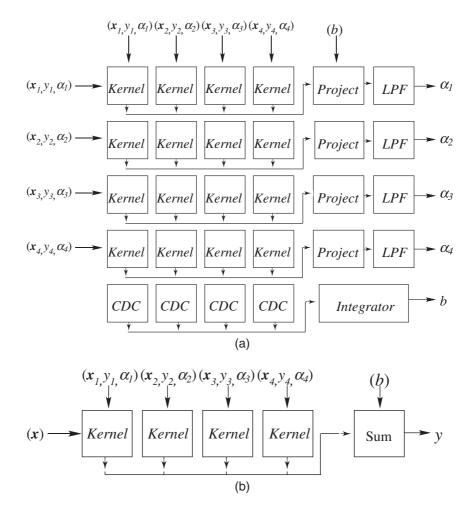

| Figure 9.1  | The schematic of the <i>Kernel</i> block                                                    | .08 |

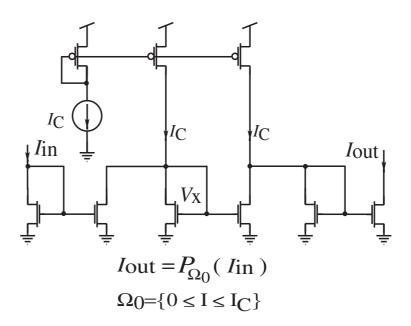

| Figure 9.2  | The schematic of the <i>Project</i> block                                                   | .09 |

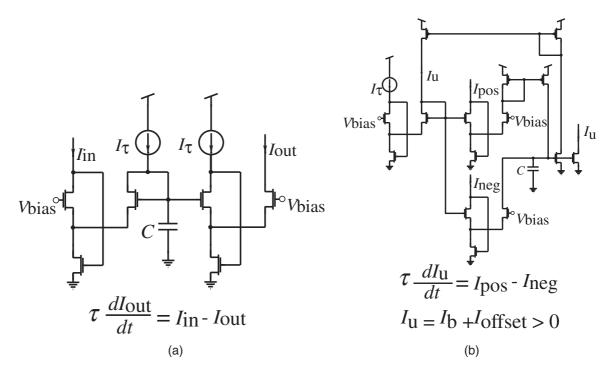

| Figure 9.3 | The schematics of the <i>LPF</i> and the <i>Integrator</i> blocks                         |

|------------|-------------------------------------------------------------------------------------------|

| Figure 9.4 | The architectures of the analog learner and classifier for SVM classification.            |

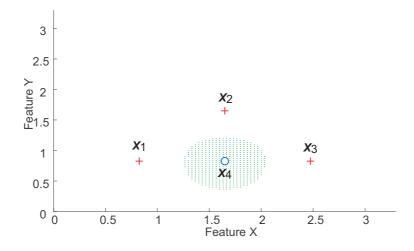

| Figure 9.5 | The distribution of the training samples                                                  |

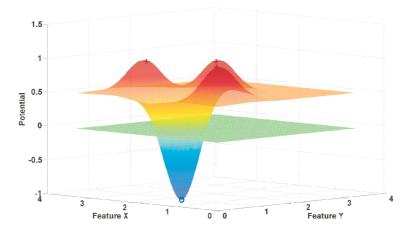

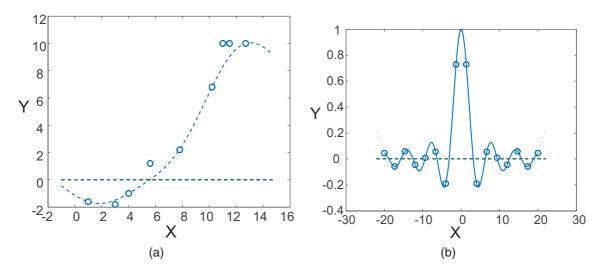

| Figure 9.6 | The simulation result of the potential level using MATLAB numerical ODE solver            |

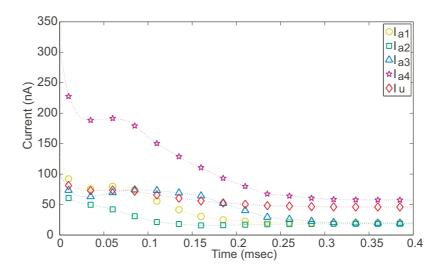

| Figure 9.7 | The transient response of the state variables simulated in SPICE 113                      |

| Figure 9.8 | The simulated output current using a SPICE circuit simulator 113                          |

| Figure 9.9 | The simulated results of the projection neural network for support vec-<br>tor regression |

#### SUMMARY

Sensory microsystems have attracted a tremendous amount of research interest because of their potential impact on a wide variety of applications. These systems receive signals through sensors and perform local signal processing to reduce the information bandwidth for subsequent transmission and conversion or to interact with the environment without explicit users' involvement. These miniaturized systems can be used in medical prosthetics or personal mobile and entertainment devices that are expected to bring significant improvement in the quality of our daily lives.

In the conventional analog-digital partitioning scheme, the power consumption has become a bottleneck factor in determining both the functionality and the feasibility of these microsystems. Although analog signal processing approaches have shown superior power efficiency, the traditional trimming techniques used to compensate for device mismatches usually consume lots of power and chip area. Besides, lack of programmability also makes analog signal processing approaches less attractive.

The ability to control the charge at floating nodes overcomes the shortcomings of conventional analog approaches and provides an additional design degree of freedom. The notion of designing circuits based on charge sensing, charge adaptation, and charge programming is explored in this research. This design concept leads to a low-power capacitive sensing interface circuit that has been designed and tested with a MEMS microphone and a capacitive micromachined ultrasonic transducer. Moreover, by using the charge programming technique, a designed floating-gate based large-scale field-programmable analog array (FPAA) containing a universal sensor interface sets the stage for reconfigurable smart sensory systems. Based on the same charge programming technique, a compact programmable analog radial-basis-function (RBF) based classifier and a resultant analog vector quantizer have been developed and tested. Measurement results have shown that the analog RBF-based classifier is at least two orders of magnitude more power-efficient than an equivalent digital processor. Furthermore, an adaptive bump circuit that can facilitate unsupervised learning in the analog domain has also been designed. A projection neural network for a support vector machine, a powerful and more complicated binary classification algorithm, has been proposed. This neural network is suitable for analog VLSI implementation and has been simulated and verified on the transistor level. These analog classifiers can be integrated at the interface to build smart sensors.

This work contributes to the reconfigurable smart sensory systems by exploring the technologies of capacitive sensing, reconfigurable analog array with universal sensor interface, and programmable analog classifiers. The results from this research have laid down the foundations for developing highly power-efficient reconfigurable smart sensory systems.

#### **CHAPTER 1**

# **RECONFIGURABLE SMART SENSORY SYSTEM**

The integration of sensors, interface circuits, and signal processing circuitry has given rise to the developments of a great diversity of sensory microsystems that are expected to bring positive and revolutionary impacts on our daily lives. This chapter describes the challenges in developing these sensory microsystems and explains how reconfigurable smart sensory systems address these issues based on the floating-gate technologies.

### 1.1 Advanced Sensory Microsystems

The advancements in silicon technologies not only have made electronic devices smaller and faster but also have enabled the fabrication of a great diversity of micromachined transducers. Today, a large number of sensors can be integrated with electronics to create a variety of innovative sensory microsystems. Such microsystems receive external signals through sensors and then perform local signal processing to refine the information for subsequent processing or to interact with the environment directly without explicit users' involvement. The block diagram of a typical sensory system is shown in Figure 1.1.

A large number of external signals received from the sensors and the tremendous computational capabilities provided by the integrated electronics give designers great opportunities to develop advanced "smart" sensory microsystems with features that cannot be

Figure 1.1. The block diagram of a typical sensory system.

achieved before. At the same time, system designers also have to face severer power constraints than ever. The available power resources in microsystems are limited because of the small form factor. Low-power operation can prolong the life time of the system or can decrease the frequency for recharge. Even in some cases that the power is supplied externally and is delivered through wires or inductive coils, the power dissipation can overheat the microsystems due to the high power density. These more stringent power constraints determine both the functionality and the feasibility of microsystems.

### **1.2 Analog Signal Processing**

Analog signal processing has shown as a promising approach to address the power issues because of its superior efficiency. From the projected trend in Figure 1.2, the power savings of the analog signal processing is equivalent to a 20 year leap in digital technology. Furthermore, if the meaningful information can be refined using analog signal processing techniques at the sensor interface, the bandwidth for subsequent transmission, conversion, and processing can be much reduced. In some cases, the analog-to-digital conversion can be avoided altogether. As a result, the system can achieve much better efficiency and can overcome the difficulties associated with the power constraints.

Although analog signal processing plays a significant role in addressing the power challenges of advanced sensory microsystems, analog design itself is difficult. Since analog circuit performance is vulnerable to fabrication imperfections, the means to compensate for device mismatches and circuit offsets is necessary. In conventional analog approaches, these techniques consume lots of power and silicon area, which wipes out many advantages of analog signal processing. Besides, lack of programmability and reconfigurability is another shortcoming of conventional analog systems. This is also one of the major reasons that analog signal processing is not as popular as digital signal processing.

Figure 1.2. Power efficiency comparisons between analog and digital signal processing [1].

## **1.3 Charge-Based Analog Design**

Floating-gate technology has been exploited to get over the shortcomings of conventional analog approaches. Floating-gate techniques enable precise charge programming on floating nodes and provide an additional degree of freedom in designing analog circuits and systems. The new freedom allows designers to make use of capacitive circuits where floating nodes exist. It also prompts the notion of charge-based analog design based on techniques of charge sensing, charge adaptation, and charge programming.

This research explores the notion of charge-based analog circuits that facilitate reconfigurable smart sensory microsystems. Inspired by a capacitive feedback circuit, a new capacitive sensing interface circuit that senses the charge variation ascribed to a varying capacitor has been designed. The output DC level of this circuit is adjusted using charge adaptation techniques. This capacitive sensing circuit can achieve low-power consumption and has a large dynamic range. The charge programming technique can be utilized to compensate for device mismatches and circuit offsets without consuming extra power. It also provides an effective and efficient way to implement analog memories. Therefore, floating-gate based analog circuits can perform highly power-efficient programmable signal processing in an advanced reconfigurable smart sensory microsystem.

## **1.4 Reconfigurable Smart Sensory Chip**

Thanks to the emerging MEMS technologies, a variety of sensors has been developed and the demands for designing their interface circuits have grown rapidly. A reconfigurable smart sensory chip would be a useful tool for fast prototyping innovative ideas of sensory microsystems. It can greatly shorten design-testing cycles and hence reduce the costs of system development.

The block diagram of a reconfigurable smart sensory chip is shown in Figure 1.3. The chip can interface with different kinds of sensors and can perform different analog algorithms for different applications. Depending on the types of sensors employed in the microsystem, appropriate interface circuits are synthesized in the universal sensor interface (USI) blocks to transduce signals received from the outside world. Components inside the configurable analog blocks (CABs) are configured to perform feature extraction or other analog signal processing tasks. Resultant features can be fed to a programmable analog classifier for further information refinement. The reconfigurability of the chip is achieved by the interconnect network that connects component terminals to form different circuit topologies.

This chip offers sensor specialists a fast way to test their sensors and provides signal processing experts a programmable platform to perform different power-efficient analog algorithms. Because the output signals are no longer raw data but refined meaningful information, the required processing burdens of subsequent stages can be greatly lessened and the entire system can be very power efficient. This research focuses on the developments of interface circuits and analog classifiers that are critical building blocks of a reconfigurable smart sensory system.

Floating-gate transistors are versatile in the reconfigurable smart sensory chip. They

Figure 1.3. The block diagram of a reconfigurable smart sensory chip.

are utilized as compact switches in the interconnect network, as programmable elements in USI and CABs, and as analog memories in analog classifiers. Therefore, this dissertation begins with Chapter 2 presenting some capacitive circuits and an overview of floating-gate technologies. Chapter 3 describes a detail analysis, measurement results, comparisons, and a design procedure of a proposed low-power capacitive feedback charge amplifier for capacitive sensing. This approach has been applied to audio and to ultrasonic applications. The ultrasonic results are discussed in Chapter 4. In Chapter 5, a large-scale fieldprogrammable analog array (FPAA) with integrated universal sensor interface blocks are presented. In Chapter 6, a fundamental analog circuit used in analog classifiers for similarity measure is introduced. This floating-gate circuit has been used to implement a compact and power-efficient analog radial-basis-function-based classifier that is presented in Chapter 7. An adaptive vector quantizer that can perform unsupervised learning is described in Chapter 8. In Chapter 9, a projection neural network for a more complicated binary classifier, the support vector machine, is presented. This projection neural network can be implemented in analog circuits without using any resistors or operational amplifiers and is suitable for large-scale implementations. The main contributions and key milestones that have been achieved in this work are summarized in Chapter 10.

#### **CHAPTER 2**

# **PROGRAMMABLE ANALOG TECHNOLOGIES**

Analog signal processing is an attractive approach to developing microsystems because of its superior power efficiency. However, it is not trivial to design analog processors performing accurate computation in the presence of device mismatches. Traditional design techniques used to compensate for fabrication imperfections usually consume tremendous amounts of power and die area, which annuls many of the benefits of analog signal processing. Lack of programmability and reconfigurability is another drawback of conventional analog systems. Recently, floating-gate technologies have been shown as powerful tools to circumvent these shortcomings. Floating-gate transistors have been successfully utilized to trim out amplifier offsets [2], to build data converters [3], to generate programmable references [4], and to make large-scale programmable analog signal processing systems possible [1,5].

This chapter starts with introducing some capacitive circuits that are associated with floating-gate transistors as well as a capacitive sensing interface circuit proposed in this research. An overview of floating-gate transistors including the structure and the characteristics is then presented. Techniques to precisely program an array of floating-gate transistors are also detailed in this chapter.

#### 2.1 Capacitive Circuits

The capacitive circuit approach is a practical and efficient technique for integrated circuit designers because capacitors are natural elements in a CMOS process. Unlike resistors, capacitors neither dissipate DC power nor do they contribute thermal noise. However, in conventional circuit design, capacitive circuits that include some floating nodes are usually avoided because the charges on the floating nodes are neither predictable nor controllable. Recently, charges on the floating nodes can be precisely programmed using floating-gate

technologies. As a result, capacitive circuits that can effectively calculate the weighted summation of voltages are no longer prohibitive.

If the initial conditions of floating-node charges are not given, Kirchhoff's current and voltage laws are not enough to analyze capacitive circuits. A capacitive circuit needs to be described using the principle of charge conservation. A capacitive voltage divider is shown in Figure 2.1a. If Kirchhoff's current law is used to derive the output voltage, the equality will be given as

$$sC_1(V_{\rm in} - V_{\rm out}) = sC_2V_{\rm out}.$$

(2.1)

Apparently the DC output voltage cannot be determined by (2.1) because  $s = j\omega = 0$  at DC. If  $V_{out}$  is a floating node and the charge conservation principle is applied to that node, the resultant equality can be expressed as

$$Q = C_1(V_{\rm out} - V_{\rm in}) + C_2 V_{\rm out}.$$

(2.2)

The output voltage can then be derived as

$$V_{\rm out} = \frac{C_1 V_{\rm in} + Q}{C_1 + C_2}$$

(2.3)

$$= \frac{C_1 V_{\rm in}}{C_1 + C_2} + V_{\rm Q}.$$

(2.4)

The output voltage expression, (2.4), of Figure 2.1a is similar to that of a resistive voltage divider. The difference is the extra voltage term,  $V_Q = Q/(C_1 + C_2)$ , set by the charge at the output floating node.

A more general capacitive circuit with multiple inputs is illustrated in Figure 2.1b. The charge conservation principle can also be applied and the equality is given as

$$Q = C_1(V_{\rm fg} - V_1) + C_2(V_{\rm fg} - V_2) + \dots + C_n(V_{\rm fg} - V_n).$$

(2.5)

The resultant expression of the floating-node voltage is

$$V_{\rm fg} = \frac{C_1 V_1 + C_2 V_2 + \dots + C_n V_n + Q}{C_1 + C_2 + \dots + C_n}$$

(2.6)

$$=\frac{C_1V_1+C_2V_2+...+C_nV_n}{C_{\rm T}}+V_{\rm Q}.$$

(2.7)

Figure 2.1. The schematics of two capacitive circuits. (a) A capacitive voltage divider (b) A capacitive voltage summation

From (2.7), the operation of weighted voltage summation can be easily implemented in Figure 2.1b without consuming DC power.

The capacitive circuit can also be used to form a feedback around an amplifier, as shown in Figure 2.2a. Again, the equality of the charge conservation on the floating node can be expressed as

$$Q = C_1(0 - V_{\rm in}) + C_2(0 - V_{\rm out}), \qquad (2.8)$$

and the output voltage can be expressed as

$$V_{\rm out} = -\frac{C_1 V_{\rm in} + Q}{C_2}$$

(2.9)

$$= -(\frac{C_1}{C_2}V_{\rm in} + V_{\rm Q}). \tag{2.10}$$

The closed-loop gain is  $-C_1/C_2$ , as expected. There is also a charge dependent term,  $V_Q = Q/C_2$ , in the output voltage expression.

Traditionally, floating-node approaches have been avoided by circuit designers because the charge on a floating node is neither predictable nor controllable. With recent advancements in floating-gate techniques, charges on floating nodes now can be adjusted or programmed [6,7] and, as a result, capacitive circuits are no longer prohibitive. Stemming

Figure 2.2. The schematics of two capacitive feedback circuits. (a) A capacitive voltage amplifier (b) A capacitive sensing charge amplifier

from the circuit in Figure 2.2a, the capacitive circuit in Figure 2.2b has been proposed as a low-power capacitive sensing circuit that will be detailed in the subsequent chapter.

## 2.2 Floating-Gate Transistor

A floating-gate transistor is a normal transistor with the gate that has no DC path to a fixed voltage. One or multiple external voltages are capacitively coupled into the floating gate. The layout and the circuit schematic of a pFET floating-gate transistor with two input capacitances are shown in Figure 2.3a. The floating gate is made up of the poly1 layer and is surrounded by high-quality silicon-oxide. Under normal operating conditions, the charge stored on the floating gate cannot escape and, therefore, the floating-gate transistor can be used as a non-volatile memory device. The external voltages are applied to the poly2 layers and are capacitively coupled into the floating gate via poly-poly capacitances. If the parasitic capacitance from the n-well to the poly gate is neglected, the floating-gate voltage in Figure 2.3a can be expressed as

$$V_{\rm fg} = \frac{C_1 V_{\rm in1} + C_2 V_{\rm in2} + C_{\rm tun} V_{\rm tun} + Q}{C_1 + C_2 + C_{\rm tun}}.$$

(2.11)

Charge on the floating-gate can be adjusted using hot-electron injection and Fowler-Nordheim tunneling. The tunneling mechanism takes place at a tunneling capacitor that is made from poly-silicon and a separate n-well.

Figure 2.3. The circuit schematic, layout, and symbol of a pFET floating-gate transistor with two input capacitances.(a) The circuit schematic and the layout(b) The symbol

From (2.11), a single floating-gate transistor performs the operation of weighted summation of voltages and also functions as an analog memory. Therefore, it is a versatile computation and storage device for analog signal processing. If the input coupling capacitances in Figure 2.3a are matched and the tunneling capacitance as well as other parasitic capacitances is negligible, (2.11) can be approximated as

$$V_{\rm fg} \approx \frac{1}{2} V_{\rm in1} + \frac{1}{2} V_{\rm in2} + V_{\rm Q},$$

(2.12)

where  $V_Q = Q/C_T$  and  $C_T$  is the total capacitance seen from the floating gate. This twoinput floating-gate transistor, the symbol of which is shown in Figure 2.3b, has been utilized in developing compact analog classifiers in this research.

## 2.3 Floating-Gate Programming

The charge stored on a floating gate is insulated by surrounding oxide. To move the charge across the oxide energy barrier, Fowler-Nordheim tunneling and channel hot electron injection mechanisms are used.

Tunneling arises from the fact that an electron wave function has finite extent. If the energy barrier is thin enough, the extent is sufficient for an electron to penetrate the barrier.

Figure 2.4. The conduction band diagram for tunneling process.

In a tunneling capacitor, the energy barrier of the oxide prevents electrons on the floating gate from jumping to the n-well. If the tunneling voltage is raised, a high electric field across the tunneling capacitor results in decrease of effective thickness of the barrier, which increases the probability of electrons crossing the oxide, as shown in Figure 2.4. In this manner, Fowler-Nordheim tunneling removes electrons from the floating gates through the tunneling capacitor. The tunneling current can be modeled [8] by

$$I_{\rm tun} = I_0 e^{-\frac{t_{\rm ox} \mathcal{E}_0}{V_{\rm tun} - V_{\rm fg}}},$$

(2.13)

where  $\mathcal{E}_0$  is a device parameter. Because of poor selectivity, tunneling currents are used as a global erase. The tunneling voltage used for floating-gate transistors fabricated in a 0.5  $\mu$ m process is above 15 V.

Channel hot electron injection can transfer electrons from the channel of a MOS transistor to the floating gate. There are two necessary conditions for hot electron injection: sufficient amount of channel current and a high electric field across the channel and the drain terminal. The injection process is illustrated in Figure 2.5. When holes in a pFET transistor travel from the source to the drain, they will be accelerated in the channel-drain depletion region. If the electric field between the channel and the drain is large enough, the holes will cause impact ionization and will generate hot hole-electron pairs. The energy of these hot electrons can be so high that some hot electrons can jump cross the oxide barrier onto the floating gate. Other electrons will flow to the bulk and become bulk current. The

Figure 2.5. The band diagram for channel hot electron injection process.

hot-electron injection current can be modeled [7, 8] as

$$I_{\rm inj} = I_{\rm inj0} \left(\frac{I_{\rm s}}{I_{\rm s0}}\right)^{\alpha} e^{-\Delta V_{\rm ds}/V_{\rm inj}},\tag{2.14}$$

where  $I_s$  is the channel current,  $V_{inj}$  is a device and bias dependent parameter, and  $\alpha$  is very close to 1.

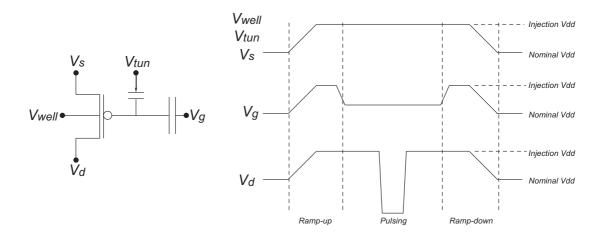

To enable the injection, the voltage between the source and drain needs to be larger than the nominal  $V_{DD}$  so that there exists sufficient channel-drain voltage drop for impact ionization. To prevent accidental injection, all terminals of the floating-gate transistor are raised to the injection  $V_{DD}$ , which is about 6.5 V for a 0.5  $\mu$ m CMOS process, during the ramp-up phase. To activate precise injection, the input gate voltage is adjusted to provide enough channel current and a short voltage pulse is applied to the drain. The injection takes place in this pulsing phase. Usually, the pulse width is fixed and the pulse height can be predicted algorithmically. After the injection, all terminal voltages are decreased by the same amount and the source voltage is back to the nominal  $V_{DD}$ . A time diagram of the injection process is shown in Figure 2.6. Measured floating-gate characteristics after tunneling and injection are shown in Figure 2.7. Programming the charge on the floating gate is equivalent to adjusting the threshold voltage of a transistor. Therefore, precise

Figure 2.6. The time diagram of injection process.

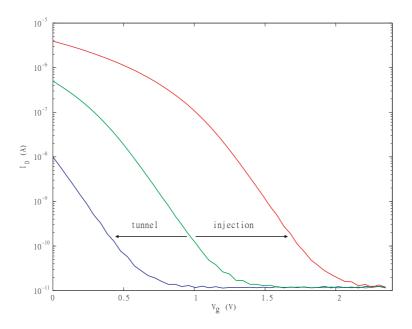

Figure 2.7. The measured I-V curves after tunneling and injection [1].

floating-gate programming can be an effective way to compensate for threshold voltage mismatches.

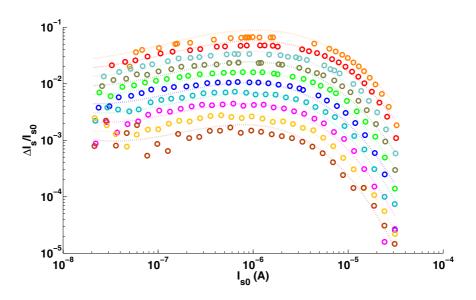

To predict the required pulse depth for precise programming, an empirical model for injection proposed in [9] is used. Given a short pulse of  $V_{ds}$  across a floating-gate device, the injection current is proportional to  $\Delta I_s/I_{s0}$ , where  $\Delta I_s = I_s - I_{s0}$  is the increment of the channel current. From (2.14), the logarithm of this ratio should be a linear function of  $V_{ds}$  and a nonlinear function of  $\log(I_{s0}/I_u)$ , where  $I_u$  is an arbitrary unity current. It can be

Figure 2.8. Measured injection characterization points (circles) and the corresponding curve fits (dashed lines).

expressed as

$$\log\left(\frac{\Delta I_{\rm s}}{I_{\rm s0}}\right) = g\left(\log\left(\frac{I_{\rm s0}}{I_{\rm u}}\right)\right) V_{\rm ds} + f\left(\log\left(\frac{I_{\rm s0}}{I_{\rm u}}\right)\right),\tag{2.15}$$

where  $g(\cdot)$  and  $f(\cdot)$  are weakly linear functions when the transistor is in the subthreshold region and are nonlinear when the transistor is in the above-threshold region. Before the programming process, a floating-gate characterization process is performed. In the characterization process,  $V_{ds}$  and  $I_{s0}$  are given and  $\Delta I_s$  can be measured. Thus,  $g(\log(I_{s0}/I_u))$ and  $f(\log(I_{s0}/I_u))$  can be regressed by high-order polynomial functions. After the characterization process, the resultant polynomial functions,  $\hat{f}(\log(I_{s0}/I_u))$  and  $\hat{g}(\log(I_{s0}/I_u))$ , are obtained. In the programming process, with these polynomial functions, the appropriate  $V_{ds}$  value for injection can be predicted by

$$V_{\rm ds} = \frac{\log\left(\frac{\Delta Is}{I_{\rm s0}}\right) - \hat{f}\left(\log\left(\frac{I_{\rm s0}}{I_{\rm u}}\right)\right)}{\hat{g}\left(\log\left(\frac{I_{\rm s0}}{I_{\rm u}}\right)\right)},\tag{2.16}$$

where  $I_{s0}$  is the given starting point and  $I_s$  is the target value.

Measured and regression results for the injection characteristics are compared in Figure 2.8. Here, the polynomial functions are cubic and the pulse width is fixed at  $200\mu$ sec.

Figure 2.9. Floating-gate array programming.

10 different values of  $V_{ds}$  ranging from 5.6V to 6.5V and 30 channel current levels ranging from 20nA to 20 $\mu$ A are used to obtain the curve fits for each curve. To avoid overshooting the target value, we always apply slightly shorter and smaller pulses to the drain than the predicted values. Therefore, despite the mismatches and the discrepancy between the curve fits and the measured data, the current level of the floating-gate transistor approaches the target value asymptotically. The current level can be programmed within 0.5% of the target.

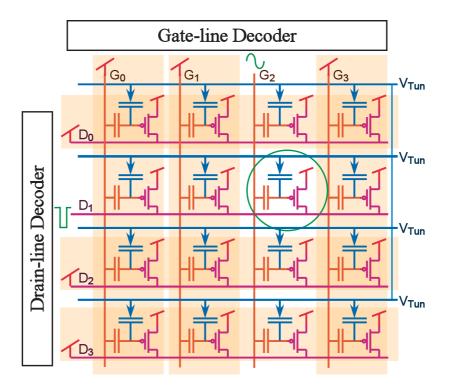

To program an array of floating-gate transistors, the devices are arranged into a twodimensional array in programming mode, as shown in Figure 2.9. All the source terminals are connected to  $V_{DD}$ . The gate coupling voltages and the drain voltages are switched between a  $V_{DD}$  and the outputs of digital-to-analog converters. The decoders select which device is connected to the DAC voltages. Because two conditions, sufficient channel current and a high channel-to-drain field, are required for injection, the unselected columns (or rows) can be deactivated by applying  $V_{DD}$  to the corresponding gate-lines (or drain-lines) so that there is no current through (or no field across) the devices for injection. In this manner, each floating-gate transistor can be isolated from others and can be programmed individually.

In this topology, the maximum number of electrons that can be injected into a floatinggate transistor is limited by the current isolation rule. If there are too many electrons on a floating-gate transistor, the source current is not negligible when the external coupling voltage is  $V_{DD}$ . If the drain-line is pulsed to program another floating-gate transistor in the same row, the unselected floating-gate transistor will also be injected. To avoid this problem, an extra pFET transistor can be used as a switch to shut the source current down completely when a row is not selected.

### **CHAPTER 3**

# A CHARGE-BASED LOW-POWER CAPACITIVE SENSING INTERFACE CIRCUIT

This chapter presents a low-power approach to capacitive sensing that can achieve a high signal-to-noise ratio. The circuit is composed of a capacitive feedback charge amplifier and a charge adaptation circuit. Without the adaptation circuit, the charge amplifier only consumes 1  $\mu$ W and achieves an SNR of 69.34 dB in the audio band. An adaptation scheme using Fowler-Nordheim tunneling and channel hot electron injection mechanisms to stabilize the DC output voltage is demonstrated. This scheme provides a low-frequency corner at 0.2 Hz. The measured noise spectra show that this slow adaptation does not degrade the circuit performance. The DC path can also be provided by a large feedback resistance without causing extra power consumption. A charge amplifier with a MOS-bipolar nonlinear resistor feedback scheme is interfaced with a capacitive micromachined ultrasonic transducer to demonstrate the feasibility of this approach to ultrasound applications.

## **3.1** Challenges in Capacitive Sensing

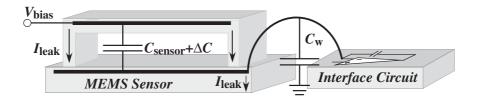

Capacitive transduction is widely used in sensory microsystems to detect force, pressure, as well as position, velocity, or acceleration of a moving object. In a typical two-chip hybrid approach, as shown in Figure 3.1, there is a parasitic capacitance at the interconnect

Figure 3.1. The block diagram of a two-chip hybrid approach.

Figure 3.2. The block diagram of the capacitive sensing.

resulting from bonding wires and pads. The parasitic capacitance and the static sensor capacitance are usually much larger than the varying capacitance to be sensed. Additionally, some unpredictable and undesired leakage currents exist at the sensor-electronics interface. Designing a capacitive sensing interface circuit that has a large dynamic range and high sensitivity is not a trivial task. It becomes more challenging to design interface circuits for low-power applications.

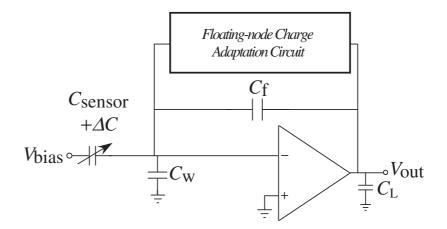

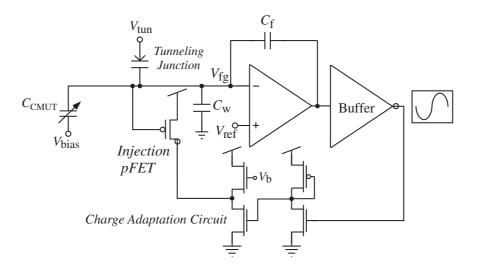

In this chapter, a new approach to sensing capacitive changes is proposed. As shown in Figure 3.2, the circuit is composed of a capacitive feedback charge amplifier and a charge adaptation circuit. The charge amplifier operates continuously in time and can be viewed as a capacitive circuit. To cope with the charge and leakage currents at the floating node, methods based on floating-gate circuit techniques [6, 7, 10] are employed to adapt the charge. The analysis given in this chapter starts from a capacitive feedback charge amplifier without the charge adaptation circuit. The complete analysis with the charge adaptation will be presented in Chapter 4.

# 3.2 Capacitive Sensing Charge Amplifier

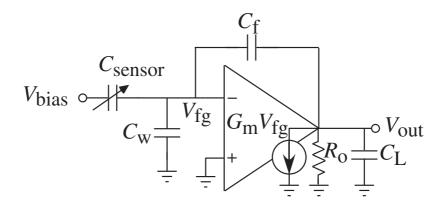

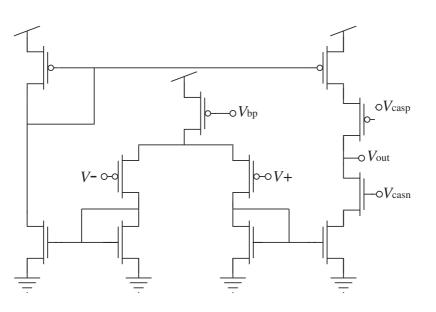

The small-signal model of a capacitive feedback charge amplifier without the chargeadaptation circuit is shown in Figure 3.3. The amplifier is modeled as a first-order system. The topology can be a simple cascode operational transconductance amplifier (OTA), as

Figure 3.3. The small-signal model of a capacitive sensing charge amplifier.

shown in Figure 3.4, a folded cascode amplifier, or a cascode common-source amplifier. If the amplifier has two stages, although similar results can be derived, the dominant pole will depend on the compensation capacitance and the power consumption will be larger.

#### **3.2.1** Transfer function

The DC output voltage can be expressed as

$$V_{\rm out} = -\frac{V_{\rm bias}C_{\rm sensor} + Q}{C_{\rm f}(1+\rho)},\tag{3.1}$$

Figure 3.4. The schematic of a single-stage cascode operational transconductance amplifier.

where  $\rho = C_T/(C_f A_v)$ ,  $C_T = C_{sensor} + C_w + C_f$ ,  $A_v = G_m R_o$ , and Q is the charge on the floating node. Usually the amplifier gain should be designed high enough so that

$$A_{\rm v} \gg C_{\rm T}/C_{\rm f},\tag{3.2}$$

and

$$\rho \ll 1. \tag{3.3}$$

In this case, (3.1) can be approximated as

$$V_{\rm out} \approx -\frac{V_{\rm bias}C_{\rm sensor} + Q}{C_{\rm f}} \text{ as } \rho \to 0.$$

(3.4)

The DC level of  $V_{out}$  can be set at halfway between the rails either by adjusting the noninverting terminal voltage if the floating-gate charge is fixed, or by adjusting the floatinggate charge according to the output voltage.

The variation of the output voltage is proportional to the variation of the sensor capacitance and can be expressed as

$$\Delta V_{\text{out}} = -\frac{V_{\text{bias}}}{C_{\text{f}}(1+\rho)} \cdot \Delta C_{\text{sensor}}.$$

(3.5)

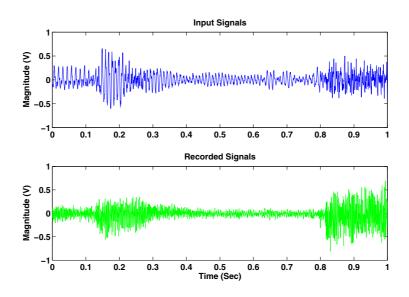

The circuit can achieve high sensitivity if a large value of  $V_{\text{bias}}$  and a small value of  $C_{\text{f}}$  are used. A recorded music waveform from a version of the capacitive sensing charge amplifier that is interfaced with an audio MEMS microphone is shown in Figure 3.5.

If the floating-node voltage is regulated by the feedback and is assumed to be constant, the transfer function of the capacitive sensing charge amplifier can be expressed as

$$\frac{V_{\text{out}}(s)}{C_{\text{sensor}}(s)} = -\frac{V_{\text{bias}}}{C_{\text{f}}(1+\rho)} \cdot \frac{1-sC_{\text{f}}/G_{\text{m}}}{1+s\tau},$$

(3.6)

where  $\tau$  is the time constant of the circuit and is given as

$$\tau = \frac{1}{\omega_{3dB}} = \frac{C_{\text{eff}}}{G_{\text{m}}(1+\rho)},\tag{3.7}$$

where  $C_{\text{eff}} = (C_{\text{o}}C_{\text{T}} - C_{\text{f}}^2)/C_{\text{f}}$ , and  $C_{\text{o}} = C_{\text{L}} + C_{\text{f}}$ . Because both  $C_{\text{sensor}}$  and  $C_{\text{L}}$  are usually larger than  $C_{\text{f}}$ , the zero caused by the capacitive feedthrough is at a much higher frequency

Figure 3.5. Measured waveform from a capacitive sensing charge amplifier.

than the amplifier bandwidth. If the amplifier gain is large enough  $(A_v \gg C_T/C_f)$ , the transfer function can be approximated as

$$\frac{V_{\text{out}}(s)}{C_{\text{sensor}}(s)} = -\frac{V_{\text{bias}}}{C_{\text{f}}} \cdot \frac{1 - sC_{\text{f}}/G_{\text{m}}}{1 + sC_{\text{eff}}/G_{\text{m}}}.$$

(3.8)

#### 3.2.2 Noise analysis

The output-referred noise power can be calculated from the small-signal model shown in Figure 3.6a. If  $V_{\rm fg}$  and  $V_{\rm out}$  are related by a capacitive divider, the small signal model can be further simplified, as shown in Figure 3.6b, where  $R_{\rm x} = C_{\rm T}/(C_{\rm f}G_{\rm m})$ . The output-referred voltage noise can be expressed as

$$\hat{V}_{\text{out,total}}^2 = \frac{\tilde{i}_o^2}{4G_{\text{m}}} \cdot \frac{C_{\text{T}}}{C_{\text{f}}C_o} \cdot \frac{1}{1+\rho}$$

(3.9)

$$= \frac{nqU_{\rm T}}{2\kappa} \cdot \frac{C_{\rm T}}{C_{\rm f}C_{\rm o}} \cdot \frac{1}{1+\rho}.$$

(3.10)

In (3.10), the differential pair transistors are assumed operating in the subthreshold region and

$$\tilde{i}_{\rm o}^2 = \frac{2}{\kappa} nq U_{\rm T} G_{\rm m} \quad (A^2/{\rm Hz}), \tag{3.11}$$

where  $\kappa$  is the subthreshold slope factor of a MOS transistor, *n* is the effective number of noisy transistors, *q* is the charge of an electron,  $U_{\rm T}$  is the thermal voltage, and  $G_{\rm m}$  is the transconductance of the transistor in the differential pair. This result is consistent with that in [11], where the transistors are assumed to operate in the above-threshold region.

Figure 3.6. The small-signal models of the capacitive sensing charge amplifier for noise analysis. (a) The small-signal model for noise analysis (b) Simplified small-signal model for noise analysis

#### 3.2.3 Maximum dynamic range

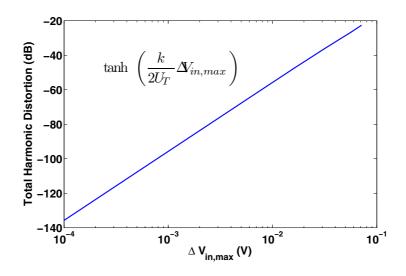

The nonlinearity of the circuit is assumed to come from the voltage-controlled current source of the transconductance amplifier. When the input voltage is smaller than or equal to the maximum input linear voltage,  $\Delta V_{\text{lin,max}}$ , the output current is linear in the input voltage with some tolerable distortion. For example, if the OTA shown in Figure 3.4 is employed in the charge amplifier and the differential pair operates in the subthreshold region, the I-V

Figure 3.7. Nonlinearity of an OTA.

relation can be expressed as

$$I_{\rm out} = I_{\rm b} \tanh\left(\frac{\kappa V_{\rm d}}{2U_{\rm T}}\right) \tag{3.12}$$

$$\approx I_{\rm b} \frac{\kappa \Delta V_{\rm fg}}{2U_{\rm T}},\tag{3.13}$$

where  $I_b$  is the tail current and  $V_d$  is the OTA input differential voltage. The hyperbolictangent function gives rise to the nonlinearity of the circuit. The relation between the total harmonic distortion and the maximum input linear range of the differential pair is plotted in Figure 3.7. If  $V_d \leq \Delta V_{\text{lin,max}} = 8 \text{ mV}$ , the approximation of

$$G_{\rm m} \approx \frac{\kappa I_{\rm b}}{2U_{\rm T}}$$

(3.14)

brings about -60 dB total harmonic distortion when  $U_T = 25 \text{ mV}$  and  $\kappa = 0.7$  are used in (3.12).

The maximum output linear range,  $\Delta V_{out,max}$ , can be obtained from the transfer function of  $V_{fg}$  to  $V_{out}$  as

$$\begin{aligned} \left| \Delta V_{\text{out,max}}(j\omega) \right| &= \left| \frac{(j\omega)C_{\text{f}} - G_{\text{m}}}{(j\omega)C_{\text{o}} + G_{\text{m}}/A_{\text{v}}} \Delta V_{\text{fg}}(j\omega) \right| \\ &\leq \left| \frac{(j\omega)C_{\text{f}} - G_{\text{m}}}{(j\omega)C_{\text{o}} + G_{\text{m}}/A_{\text{v}}} \right| \Delta V_{\text{lin,max}}. \end{aligned}$$

(3.15)

A normalized variable,  $\eta$ , can be defined as

$$\eta = \omega/\omega_{3dB} = \omega\tau. \tag{3.16}$$

The expression of (3.15) can be rewritten as

$$\left|\Delta V_{\text{out,max}}(\eta)\right| \le \frac{C_{\text{T}}}{C_{\text{f}}} \cdot \frac{\Delta V_{\text{lin,max}}}{\sqrt{\eta^2 (1+\rho)^2 + \rho^2}}.$$

(3.17)

If the gain of the amplifier and the bandwidth of the circuit are both infinite (i.e.  $\rho = 0$  and  $\eta = 0$ ), from (3.17), then the maximum output linear range is also infinite. The circuit is completely linear in this ideal scenario, if the limitations from supply rails do not come into play.

In reality, the amplifier has a high but finite gain  $(0 < \rho \ll 1)$  and, to save power, the operating frequency is usually close to and within the bandwidth  $(\eta \approx 1)$ . In this case, we can approximate (3.17) as

$$\left|\Delta V_{\text{out,max}}(\omega)\right| \le \frac{G_{\text{m}}}{C_{\text{o}}} \cdot \frac{\Delta V_{\text{lin,max}}}{\omega}.$$

(3.18)

From (3.18), the output linear range can be increased by increasing the  $G_{\rm m}$  or by decreasing the load capacitance. If the  $\Delta V_{\rm out,max}$  is defined as the maximum output linear range in the worst scenario within the bandwidth, we can have

$$\Delta V_{\text{out,max}} \equiv \inf_{0 < \omega \le \omega_{3dB}} \frac{G_{\text{m}}}{C_{\text{o}}} \cdot \frac{\Delta V_{\text{lin,max}}}{\omega}$$

$$= \frac{G_{\text{m}}}{C_{\text{o}}} \cdot \frac{\Delta V_{\text{lin,max}}}{\omega_{3dB}}$$

$$= \frac{C_{\text{T}}}{C_{\text{f}}} \cdot \Delta V_{\text{lin,max}}, \qquad (3.19)$$

which is the lower bound of the maximum output linear range.

#### 3.2.4 Signal-to-noise ratio

The lower bound of the circuit SNR can be obtained from (3.19) and (3.10) and can be expressed as

$$SNR \ge C_{\text{eff}} \cdot \frac{2\kappa\Delta V_{\text{lin,max}}^2}{nqU_{\text{T}}}.$$

(3.20)

The SNR can be expressed as a function of the ratio of the operating frequency to the 3dB frequency,  $\eta$ , and can be written as

$$SNR(\eta) = \frac{C_{\rm T}C_{\rm o}}{C_{\rm f}} \cdot \frac{2\kappa\Delta V_{\rm lin,max}^2}{nqU_{\rm T}} \cdot \frac{1+\rho}{\eta^2(1+\rho)^2+\rho^2}$$

(3.21)

$$\approx C_{\rm eff} \cdot \frac{2\kappa\Delta V_{\rm lin,max}^2}{nqU_{\rm T}} \cdot \frac{1+\rho}{\eta^2(1+\rho)^2+\rho^2}$$

(3.22)

$$\approx \frac{G_{\rm m}}{\omega_{3dB}} \cdot \frac{2\kappa\Delta V_{\rm lin,max}^2}{nqU_{\rm T}} \cdot \frac{1+\rho}{\eta^2(1+\rho)^2+\rho^2}.$$

(3.23)

From (3.21), if the ratio of the operating frequency to the 3dB frequency is constant, the SNR can be improved by increasing  $C_{\rm T}$ , the total capacitance seen from the floating node, by increasing the output capacitance,  $C_{\rm o}$ , or by decreasing  $C_{\rm f}$ , the feedback capacitance. To maintain the same bandwidth, more power needs to be consumed to increase the value of  $G_{\rm m}$ .

The SNR can also be expressed as a function of the frequency as

$$SNR(\omega) \approx \frac{G_{\rm m}^2}{C_{\rm eff}} \cdot \frac{2\kappa\Delta V_{\rm lin,max}^2}{nqU_{\rm T}} \cdot \frac{1}{\omega^2(1+\rho)}$$

(3.24)

From (3.24), for a given operating frequency, the SNR can be increased by increasing  $G_{\rm m}$  or by decreasing  $C_{\rm eff}$ . There exists a contradiction between (3.22) and (3.24) in the effect of  $C_{\rm eff}$  on the SNR. In (3.24), the improvement of the SNR is caused by the increase of the circuit bandwidth. If the circuit bandwidth is fixed, (3.24) can be expressed as

$$SNR(\omega) \approx C_{\text{eff}} \cdot \omega_{3dB}^2 \cdot \frac{2\kappa\Delta V_{\text{lin,max}}^2}{nqU_{\text{T}}} \cdot \frac{1}{\omega^2(1+\rho)},$$

(3.25)

where  $C_{\text{eff}}$  has the same effect as it does in (3.22).

#### 3.2.5 Measurement results

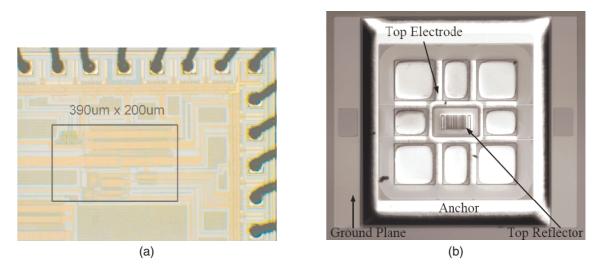

A version of the capacitive sensing circuit was fabricated in a  $0.5 \,\mu$ m double-poly CMOS process. A MEMS microphone sensor fabricated in a Sandia National Laboratory's silicon based SwIFT-Lite process [12] is used to interface with the circuit. The typical value of the sensor capacitance is in the range of pico farads. Measurement setup is shown in Figure 3.8

Figure 3.8. The setup for audio measurements.

and micrographs of the chip and sensors are shown in Figure 3.9. An ultra-thin card type speaker is used as an acoustic signal source. A tunneling junction and an indirect injection transistor are integrated on the chip as parts of the floating-node charge adaptation circuit. To measure the characteristics without any charge adaptation circuit, both tunneling and drain voltages are tied to  $V_{DD}$ . The floating-node voltage can settle slowly to an equilibrium value, which is very sensitive to the environmental electromagnetic interference. To avoid the perturbation of the floating-node voltage, the chip and the sensor are placed inside a shielding metal box. In this setup, the non-inverting terminal voltage can be carefully adjusted to set the output DC level to halfway between the rails.

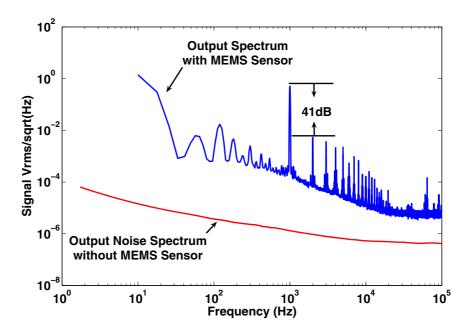

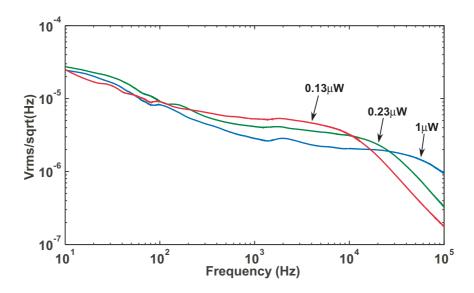

The spectrum of a output waveform with 1V magnitude at 1kHz with -38 dB total harmonic distortion is shown in Figure 3.10. The distortion comes from the offset, from the cascoded output stage of the amplifier, as well as from the nonlinearity of the speaker and of the MEMS sensor. The noise spectrum of the sensing circuit without the MEMS sensor is also shown in the same plot. The output noise depends on the input capacitance as analyzed in (3.10). To have a better idea of the circuit noise performance when it is interfaced with a MEMS sensor, the sensor is replaced with a 2 pF linear capacitor. By varying the tail current of the OTA, three noise spectrums that have power consumption of 1  $\mu$ W, 0.23  $\mu$ W, and 0.13  $\mu$ W are measured and plotted in Figure 3.11. As expected from (3.7) and (3.10), increasing the value of  $G_m$  results in a higher bandwidth with the cost of

more power consumption, but the total output thermal noise is independent of  $G_{\rm m}$ . If the sensing circuit is followed by a low-pass filter that limits the noise bandwidth inside the audio band (i.e. 20Hz to 20kHz with uniform weighting), the resulting output noise can be reduced by burning more power.

The integrated total output noise over the entire bandwidth is 570  $\mu$ V<sub>rms</sub>. The integrated thermal noise is 520  $\mu$ V<sub>rms</sub>, which is slightly higher than 370  $\mu$ V<sub>rms</sub>, the value estimated from (3.10). When the power consumption is 1  $\mu$ W, the flicker noise corner is around 2kHz, and the integrated flicker noise in that range is 225  $\mu$ V<sub>rms</sub>. The integrated total output noise in the audio band is 341  $\mu$ V<sub>rms</sub>. The corresponding minimum detectable capacitance variation in the audio band is 83 aF that is estimated from (3.8) using the parameters listed in Table 3.1. The capacitance sensitivity in the audio band is 0.59 aF/ $\sqrt{Hz}$  and the minimum detectable displacement is 20.76 × 10<sup>-4</sup> Å/ $\sqrt{Hz}$ . The SNR of the circuit is 64.88 dB over the entire bandwidth and is 69.34 dB in the audio band with the power consumption of 1  $\mu$ W.

Figure 3.9. The micrographs of the charge amplifier and the MEMS microphone sensor used in the measurement.

- (a) A die micrograph of a version of the capacitive feedback charge amplifier

- (b) The micrographs of the MEMS microphone sensor

Figure 3.10. The measured output signal and noise spectrums.

Figure 3.11. Noise spectrums of a charge amplifier with a linear input capacitor.

# 3.3 Floating-Gate-Based Charge Adaptation

In the previous section, it has been shown that using a capacitive feedback charge amplifier to sense capacitance change can achieve a high SNR with low power consumption. The performance will be compared with other approaches in the subsequent section. Although the output DC level can be set by adjusting the voltage at the non-inverting terminal, it is not stable. Without the shielding metal box, the output voltage is prone to being saturated to the supply rails because the floating-node voltage is very sensitive to the electromagnetic interference in the testing environment. In this section, floating-gate techniques are employed to stabilize the output DC level.

#### **3.3.1** Audio applications

The schematic used to demonstrate the capacitive sensing circuit with a charge adaptation circuit is shown in Figure 3.12. To reduce the leakage current caused by the ESD protection circuitry, the sensor is bonded to the chip with electronics via a bare pad. The leakage current at the connection can be integrated directly by the charge amplifier. Measured leakage current is between 5 fA and 1 pA depending on the biasing voltage and the supply rails.

A tunneling junction and an injection transistor are integrated on chip to compensate for

| CIRCUIT PARAMETERS                       |                                              |  |

|------------------------------------------|----------------------------------------------|--|

| Area                                     | $390 \times 200 \mu \mathrm{m}^2$            |  |

| Power Supply                             | 3.3V                                         |  |

| Amplifier Power Consumption              | $1\mu W$                                     |  |

| Open-Loop Gain                           | 80 dB                                        |  |

| Sensor Bias Voltage V <sub>bias</sub>    | 3.3V                                         |  |

| Feedback Capacitance $C_{\rm f}$         | 800 fF                                       |  |

| MEASUREMENT RESULTS AND PERFORMANCE      |                                              |  |

| Measured Leakage Current                 | 5 fA to 1 pA                                 |  |

| Output-referred Noise (Audio Band)       | $341\mu V_{rms}$                             |  |

| Signal to Noise Ratio (Audio Band)       | 69.34 dB                                     |  |

| Min. Detectable Capacitance (Audio Band) | 83 aF                                        |  |

| Capacitance Sensitivity @1kHz            | 0.59 aF/ <del>VHz</del>                      |  |

| Min. Detectable Displacement @1kHz       | $20.76 \times 10^{-4}$ Å/ $\sqrt{\text{Hz}}$ |  |

|                                          |                                              |  |

Table 3.1. Parameters and Measurement Results From A Capacitive Sensing Charge Amplifier

Figure 3.12. Setup for the measurement with charge adaptation scheme.

the leakage current. The injection current can be controlled by the transistor's drain voltage. One of many possible ways to control the drain voltage according to the output DC level is shown in Figure 3.12. In this adaptation scheme, the tunneling voltage is kept constant and only the injection current varies to compensate for the leakage current. The adaptation scheme can auto-zero the output DC voltage to halfway between the rails without affecting the performance of the circuit. The dynamics of these two mechanisms are detailed in [13].

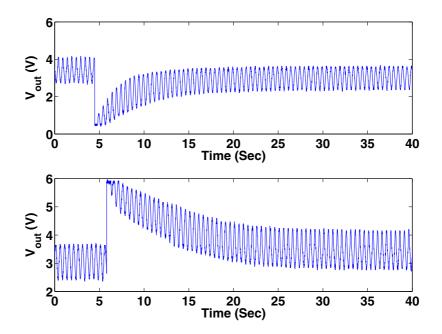

To have an enough field to generate the injection current, the supply rail is raised to 6.5 V and the externally applied tunneling voltage is 13 V. As shown in Figure 3.13, the output voltage is adapted to halfway between the rails after an upward or a downward step is applied to the sensor bias voltage. The extracted time constants are 5 seconds and 30 seconds, respectively. This implies that the effective resistance caused by the adaptation scheme is on the scale of  $10^{12} \Omega$ . Increasing the tunneling voltage results in a faster adaptation rate because of larger adaptation current.

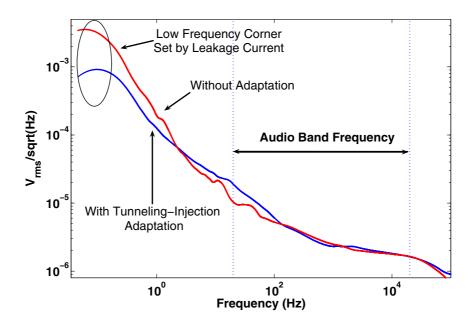

The noise spectra with and without this adaptation scheme are compared in Figure 3.14. In both cases, the circuit is interfaced with the MEMS microphone sensor. It is shown that this adaptation scheme does not degrade the noise performance over the frequency band of interest. By introducing the tunneling-injection adaptation current, the low frequency

Figure 3.13. The step responses of the capacitive sensing charge amplifier with a tunneling-injection adaptation scheme.

Figure 3.14. The measured noise spectra with and without the adaptation circuit.

corner moves slightly toward higher frequencies. The corner frequency is at 0.2 Hz and is consistent with the extracted time constants from Figure 3.13.

The power consumption in the charge adaptation circuit in Figure 3.12 is in the range

of milli-watts because the adaptation circuit is made up of discrete components. If these transistors are also integrated on chip and are designed to be long, the power consumption can be much lower. If the charge adaptation is implemented by using the topology of an autozeroing floating-gate amplifier, as proposed in [7], no extra power is consumed for the charge adaptation.

The externally applied tunneling voltage can be generated on chip using a charge pump circuit. In this case, the tunneling voltage, as well as the tunneling current, can be adjusted by the input voltage or the clock frequency of the charge pump circuit. As a result, the adaptation time constant can also be tuned on chip. Since the tunneling junction is small and the tunneling current is in the range of pico-amps, the extra cost of the silicon area and the power consumption for the charge pump circuit, including the clock generator, diodes, and capacitors, is usually low. In some applications, if the medium of the sensor is leaky and the leakage current is large enough to provide a fast adaptation time constant, the tunneling current is not necessary for charge adaptation. In this case, the circuit to generate the tunneling voltage, as well as the tunneling junction, can be avoided altogether.

#### **3.3.2** Ultrasonic applications

The charge amplifier approach has been applied to sensing capacitive micromachined ultrasonic transducers (CMUTs) that have been recently developed for ultrasound imaging [14, 15]. The measured leakage current of a CMUT device can be up to 500 pA. Since the operating frequency is high, besides the tunneling-injection adaptation scheme, a series of MOS-bipolar nonlinear resistors can be used to provide the DC path to the floating node.

A MOS-bipolar nonlinear resistor is a *p*MOS transistor with the connections from the gate to the drain and from the bulk to the source. It exhibits a very large value of resistance (exceeding  $10^{12} \Omega$ ) when the cross voltage is close to zero. The MOS-bipolar nonlinear resistor has been used in quasi-floating-gate transistor circuits [10] and the neural recording application [16]. To extend the output linearity, two nonlinear resistors in series are used to provide the DC path to the floating node.

Figure 3.15. Setup for the ultrasonic measurement.

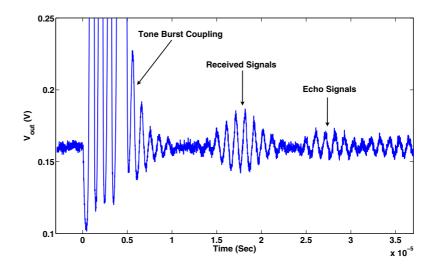

The setup for ultrasonic measurements is illustrated in Figure 3.15. A piezo transducer is used to generate plane waves at 1MHz using 16V peak 5 cycle tone bursts at its input. A CMUT receiver is biased to 90V DC at one of its terminals. The other terminal is connected to a sensing amplifier. The CMUT and the piezo device are submerged in the oil during the measurement. The capacitance of the CMUT sensor is about 2 pF and the maximum variation is about 1%. The resultant pulse-echo response is shown in Figure 3.16. The initial, highly distorted signal is due to the electromagnetic feedthrough. After 15 microseconds, the first acoustic signal arrives from the piezo transducer to the CMUT receiver. A corresponding distance is 2.2 cm in the oil, as expected. By changing this distance and the relative alignment of the piezo device and the CMUT receiver, the received signal and multiple echoes change drastically, again as expected from an ultrasound transmission experiment. Some important parameters for the CMUT measurement are listed in Table 3.2.

Figure 3.16. Measured pulse-echo waveform from an ultrasonic transducer.

| Amplifier Power Supply            | 3.3V          |

|-----------------------------------|---------------|

| CMUT Bias Voltage                 | 90V           |

| CMUT Leakage Current              | 500 pA        |

| CMUT Capacitance                  | 2 pF          |

| Piezo Transducer Frequency        | 1 <i>MHz</i>  |

| CMUT and Piezo Transducer Spacing | 2.2 <i>cm</i> |

**Table 3.2. CMUT Measurement Parameters**

## 3.4 Design Procedure

Given the specifications of the minimum detectable capacitance ( $\Delta C_{\min}$ ), the bandwidth ( $\omega_{3dB}$ ), and the SNR, we try to optimize the current consumption ( $I_b$ ), the feedback capacitance ( $C_f$ ), the load capacitance ( $C_L$ ), and the total capacitance seen from the floating node ( $C_T \approx C_{\text{sensor}} + C_w$ ). The known variables include the bias voltage for the sensing capacitor ( $V_{\text{bias}}$ ) and the maximum input linear voltage of the transconductance amplifier ( $\Delta V_{\text{lin,max}}$ ). It is also assumed that the maximum output linear range is not limited by the supply rails but only affected by the nonlinearity of the OTA.

The design starts from the sensitivity expression

$$\Delta C_{\min}^{2} = \hat{V}_{\text{out,total}}^{2} \cdot \left(\frac{C_{\text{f}}}{V_{\text{bias}}}\right)^{2}$$

$$= \frac{nqU_{\text{T}}}{2\kappa V_{\text{bias}}^{2}} \cdot \frac{C_{\text{T}}C_{\text{f}}}{C_{\text{o}}},$$

(3.26)

where  $\Delta C_{\min}$  is the minimum detectable capacitance. From (3.26) and (3.25), the conditions for  $C_{\rm T}$  and  $C_{\rm f}/C_{\rm L}$  can be given as

$$\frac{C_{\rm f}C_{\rm T}}{C_{\rm L}} \le \Delta C_{\rm min}^2 \cdot \frac{2\kappa V_{\rm bias}^2}{nqU_{\rm T}},\tag{3.27}$$

and

$$\frac{C_{\rm T}C_{\rm L}}{C_{\rm f}} \ge SNR \cdot \frac{nqU_{\rm T}}{2\kappa\Delta V_{\rm lin,max}^2}.$$

(3.28)

Therefore,

$$\frac{C_{\rm f}}{C_{\rm L}} \le \Delta C_{\rm min} \cdot \frac{2\kappa V_{\rm bias} \Delta V_{\rm lin,max}}{nq U_{\rm T} \sqrt{SNR}},\tag{3.29}$$

and

$$C_{\rm T} \ge \Delta C_{\rm min} \cdot \sqrt{SNR} \cdot \frac{V_{\rm bias}}{\Delta V_{\rm lin,max}}.$$

(3.30)

Because only the ratio of  $C_{\rm f}$  to  $C_{\rm L}$  matters, reasonable and practical values can be chosen for these two capacitances.

The next step is to determine the current consumption for a given bandwidth. Assuming that the transistors in the OTA differential pair operate in the subthreshold region, (3.14) can be substituted into (3.7) and the required current consumption can be expressed as

$$I_{\rm b} \ge \omega_{3dB} \cdot \frac{C_{\rm T}C_{\rm o}}{C_{\rm f}} \cdot \frac{2U_{\rm T}}{\kappa}.$$

(3.31)