## Switched Capacitor Circuits I

Prof. Paul Hasler Georgia Institute of Technology

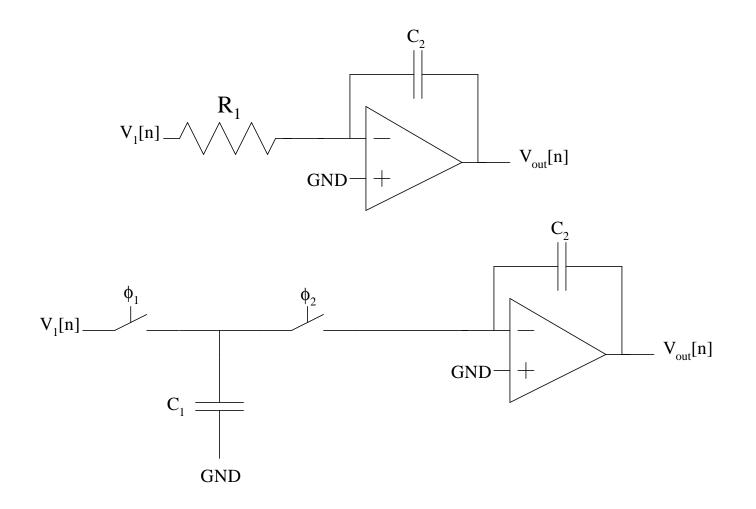

## Switched Capacitor Circuits

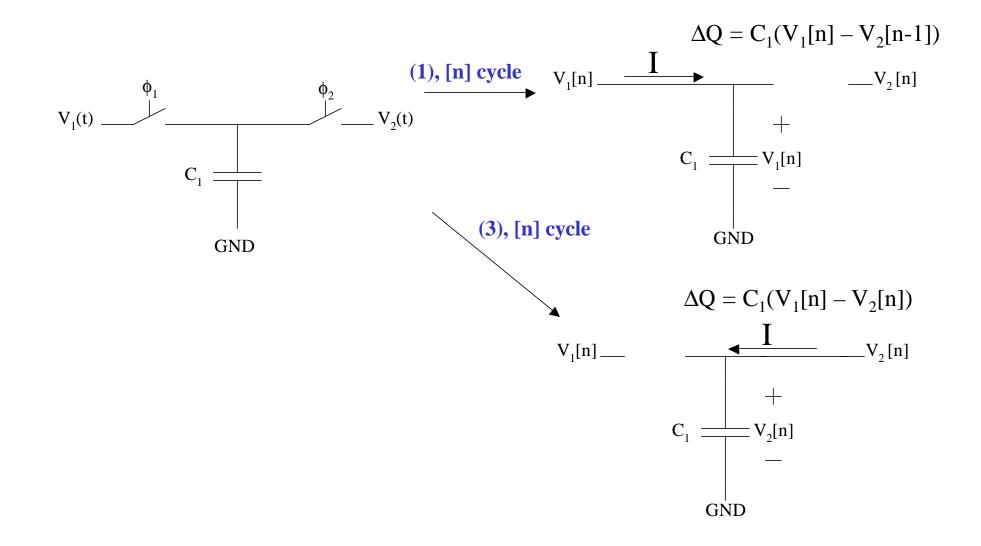

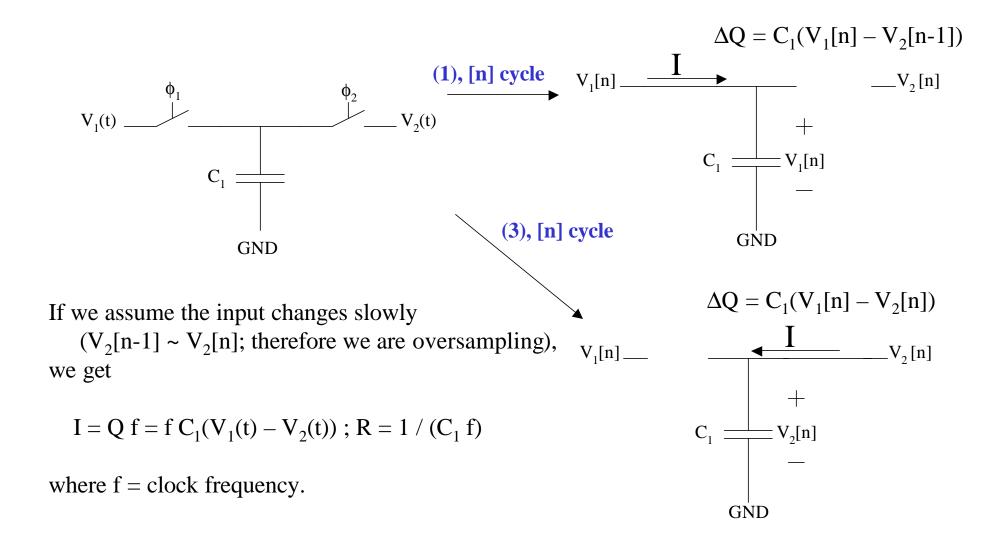

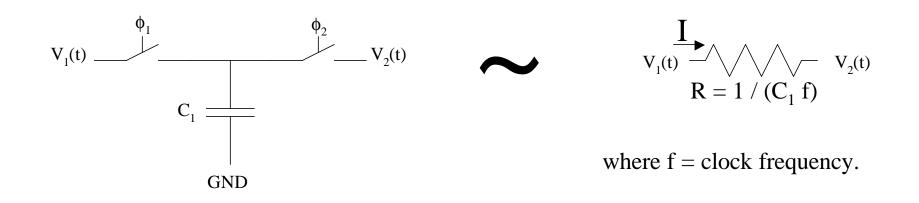

- Making a resistor using a capacitor and switches; therefore resistance is set by a digital clock and the capacitor.

- Filters built in this technology are set by external clocks, and ratio of capacitors (matching of 0.1% to 1%)

The precision of the frequency response is realized by ratios of capacitors (1% to 0.1%...better matching, larger caps; therefore more power/area), and a clock signal (which can be set precisely with a crystal reference)

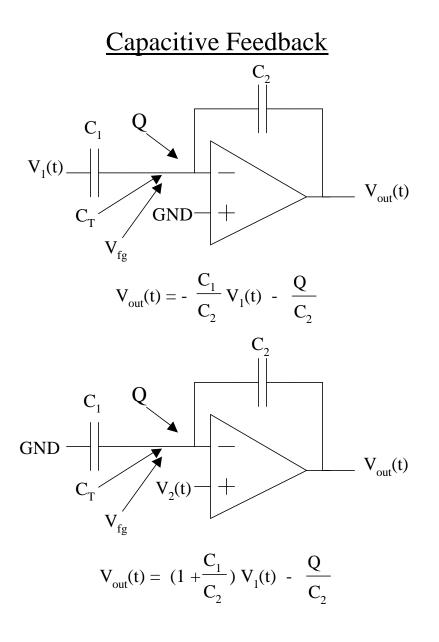

# **Capacitor Circuits**

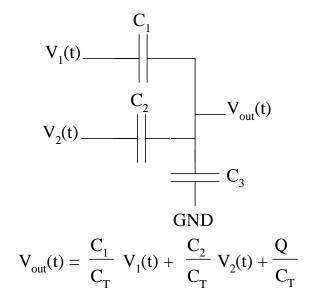

Multiple Input Voltage Divider

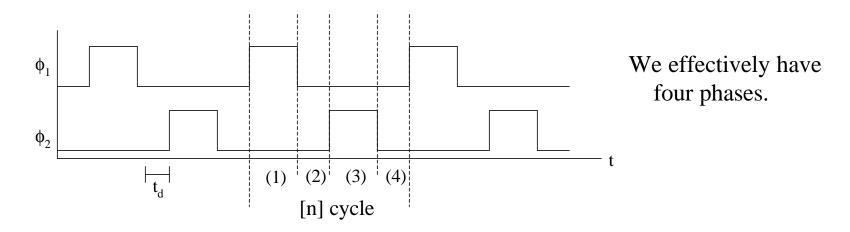

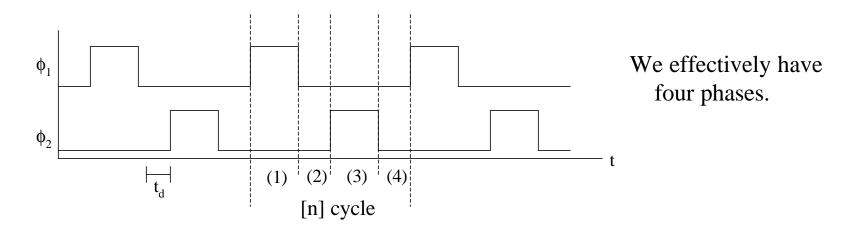

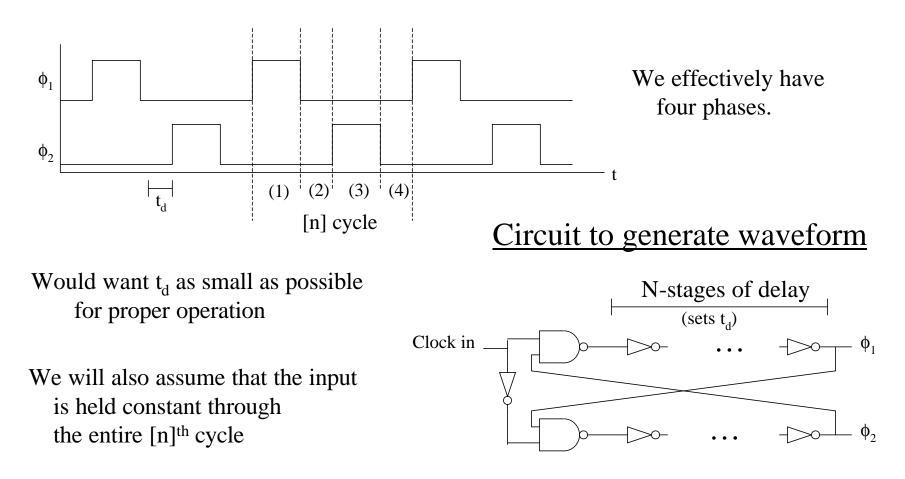

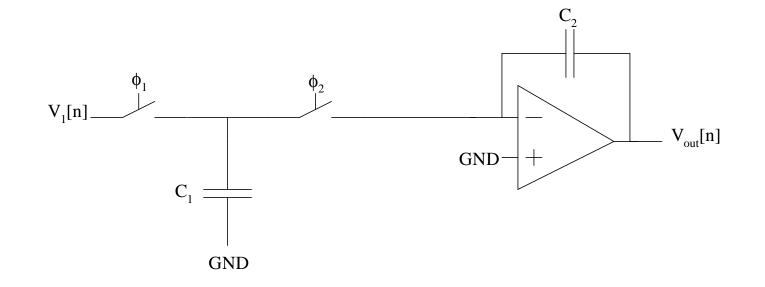

# Non-Overlapping Clocks

We will always be using non-overlapping clocks; therefore, we want a waveform like

# Non-Overlapping Clocks

We will always be using non-overlapping clocks; therefore, we want a waveform like

Would want t<sub>d</sub> as small as possible for proper operation

We will also assume that the input is held constant through the entire [n]<sup>th</sup> cycle

# Non-Overlapping Clocks

We will always be using non-overlapping clocks; therefore, we want a waveform like

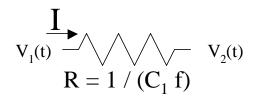

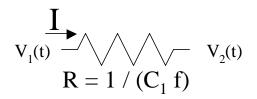

where f = clock frequency.

For 0.1pF capacitor, and a 10kHz clock, we get a resistance of 1GOhm

where f = clock frequency.

For 0.1pF capacitor, and a 10kHz clock, we get a resistance of 1GOhm

Rule of thumb: slow moving means we oversample the Nyquist frequency of the input signal by a factor of 20 or more.

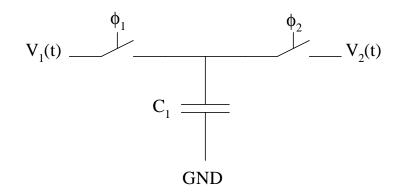

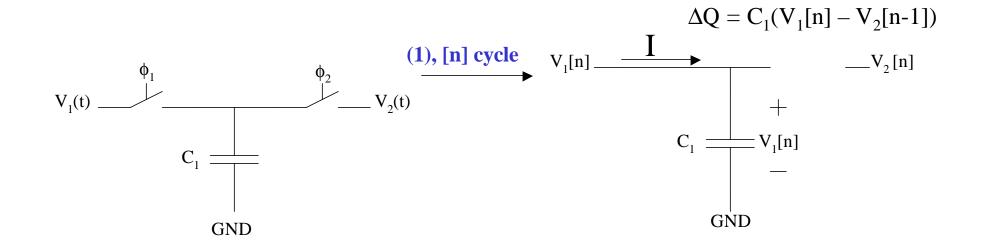

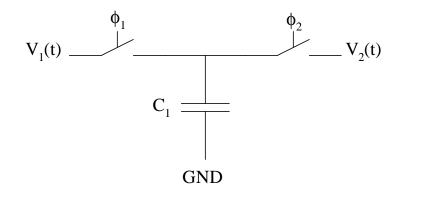

• We will step through all four phases, to get the proper result.

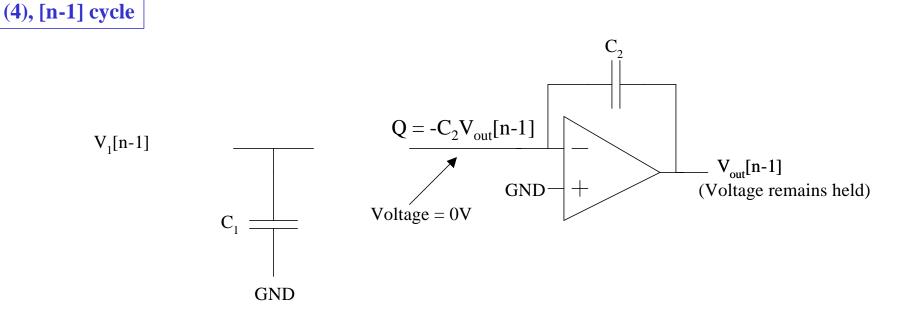

• This case is important to understand our starting point charge is stored on a capacitor ; therefore we need to know the initial state

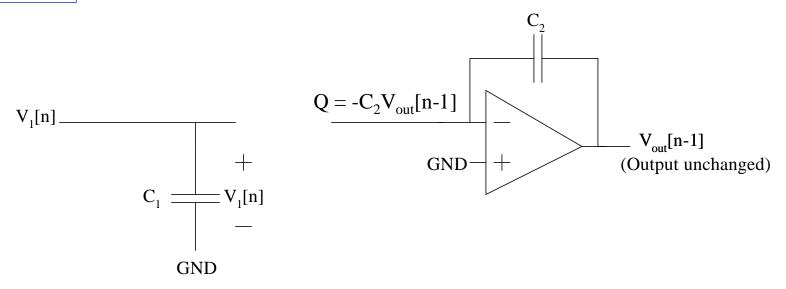

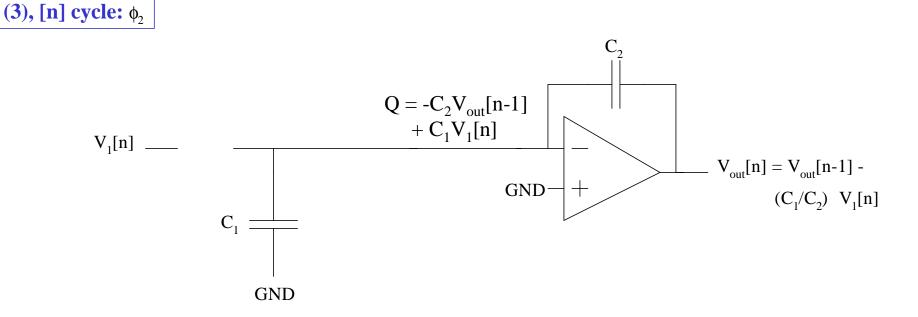

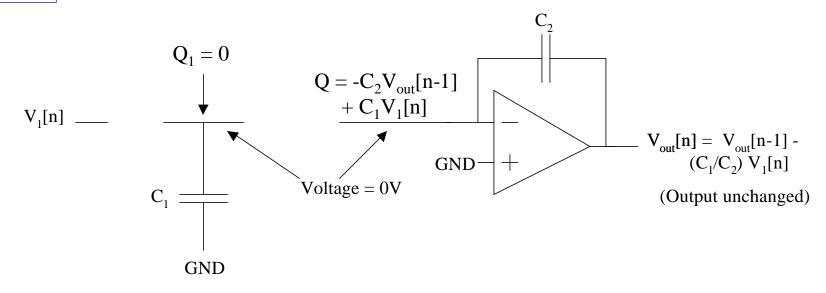

**(1), [n] cycle:** φ<sub>1</sub>

• Charge up the capacitor with voltage V<sub>1</sub>[n]

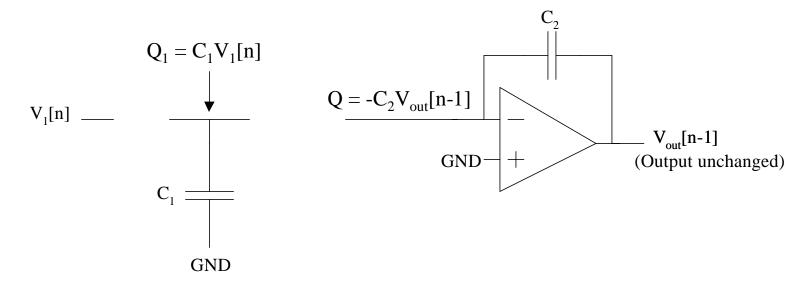

(2), [n] cycle

- We remove the capacitor from the input voltage.

- The voltage is stored across the capacitor

- We connect the capacitor to the charge summing node

- The charge initially stored on the capacitor as well as the resulting charge from the second input (V<sub>2</sub>[n]) contributes to the total charge

(4), [n] cycle

• We disconnect the capacitor from the charge summing node, and return to our initial case

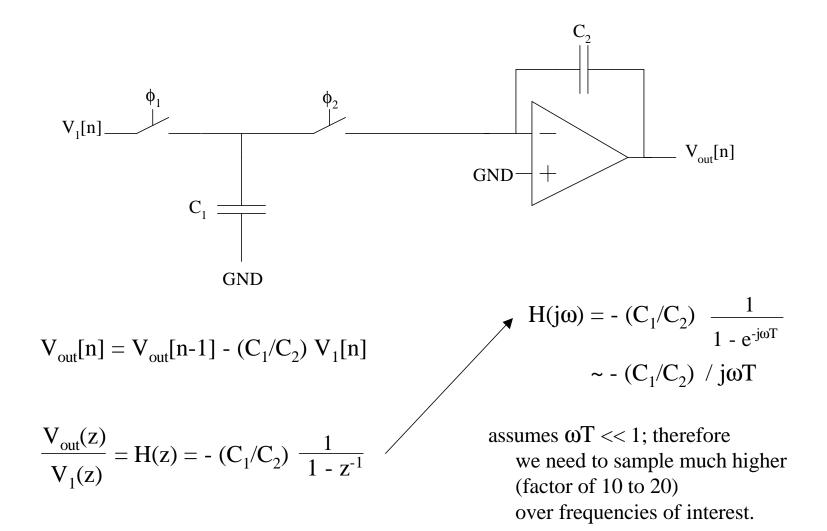

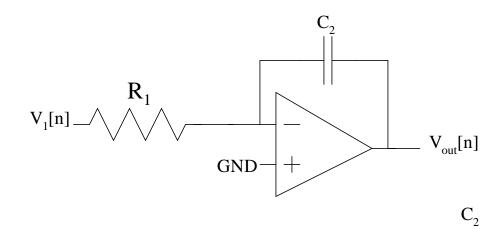

$$V_{out}[n] = V_{out}[n-1] - (C_1/C_2) V_1[n]$$

$$V_{out}[n] = V_{out}[n-1] - (C_1/C_2) V_1[n]$$

$$\frac{V_{out}(z)}{V_1(z)} = H(z) = -(C_1/C_2) \frac{1}{1 - z^{-1}}$$