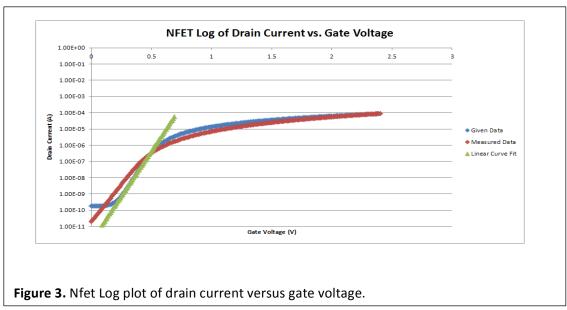

Static measurements of an NFET were taken with its source and drain held to 0 V and 2.4 V respectively whilst the gate voltage was swept from 0V to 2.4 V. In the linear region of the logarithmic plot of the drain current versus gate voltage a linear curve fit was applied to extract the slope of this linear region.

$$Slope = \frac{\kappa}{U_T} \tag{1}$$

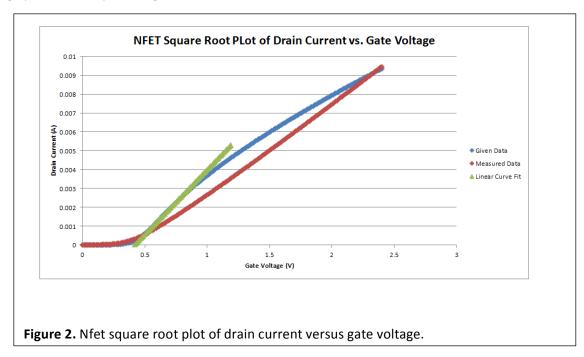

Equation (1) was solved with an assumed value of the thermal voltage,  $U_T$ , of 25.8 mV to obtain a subthreshold value for kappa of .659. The intercept was also used to obtain a value of  $I_0$  = 1.28 pA. The square root of the drain current was then plotted versus the gate voltage. A linear curve fit was then applied to this region to obtain a slope of  $S_1$  = .0069.

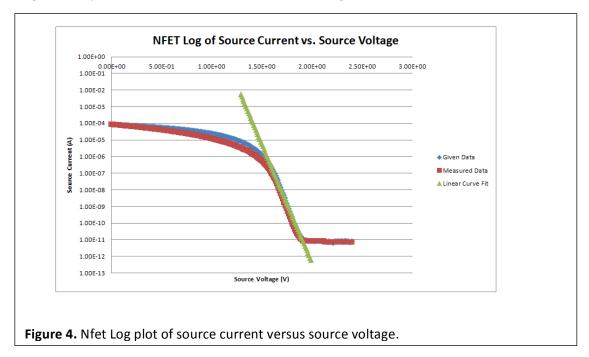

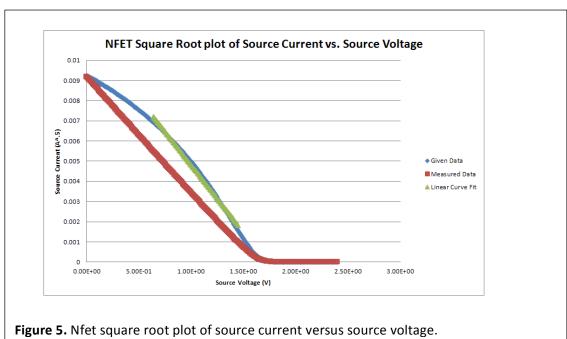

Measurements were also taken from the NFET with its gate and drain connected to 2.4 V whilst the source voltage was swept from 0 V to 2.4 V. For the logarithmic plot of source current versus source voltage, a slope of -32.796 was obtained. By inverting this slope, the actual thermal voltage was obtained of  $U_T = 30.5$  mV. This thermal voltage value differs by 18% from the assumed value of 25.8mV. In the square root plot, a slope was obtained with a value of  $S_2 = -.0043$ . Equations (2), (3) and (4) were then used to obtain a value for K and an above threshold value for kappa.

$$I = \frac{K}{2\kappa} (\kappa (V_g - V_T) - V_S)^2$$

(2)

$$S_1 = \sqrt{\frac{\kappa\kappa}{2}} \tag{3}$$

$$S_2 = -\sqrt{\frac{\kappa}{2\kappa}} \tag{4}$$

Where K was found to be 56.76  $\mu$ A/V<sup>2</sup> and kappa was found to be .652.

The linear curve fit used in the square root plot of drain current versus gate voltage was computed and extended to the X-axis to determine the value of the threshold voltage  $V_T$  = .42 V. The value of the given current at the threshold voltage was also found to give the threshold current,  $I_{th}$  = 60.598 nA.

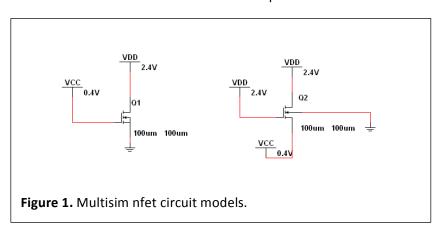

To test these parameters, Multisim was used to construct these biased transistors and then the appropriate voltage was swept and the plot was taken against the given data for each measurement. Figure 1 shows the Nfet models used in Multisim to test these parameters.

Figure 2 shows the results of the simulations of the square root of the drain current versus the gate voltage plotted on top of the given data as well as with the linear curve fits.

Whilst the curves begin in the same region, it was not possible to simulate the curved nature of the given data with a linear curve fit. This then caused the simulation results to have a linear plot as well that ended and began at the same points as the given data. Figure 3 shows the logarithmic plot of drain current versus gate voltage.

The curve fit for this plot did adequately measure the linear region, but the beginning of the measured data does not appropriately follow the given data as it should. Also please note that for the measurements shown in figures 2 and 3, the value of K was adjusted slightly to  $60 \,\mu\text{A/V}^2$  causing the

above threshold regions to have similar shapes and to end at the same current values. Figure 4 shows the logarithmic plot of source current versus source voltage.

This measured source data was far more accurate than the drain data from figures 2 and 3 in that the curves have similar shapes and remain close together throughout the plot. The linear curve fit also did measure the slope of the linear region adequately. Figure 5 shows the square root plot of source current versus source voltage.

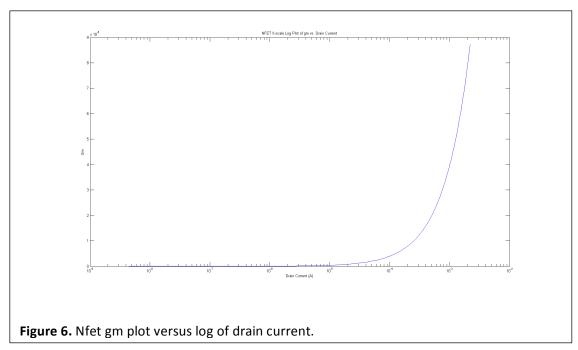

This plot had a similar issue as with the plot in figure 2 in that the given data set is not entirely linear and therefore the linear curve fit and measured data are more linear than the given data. Figure 6 shows the plot of gm versus a logarithmic drain current.

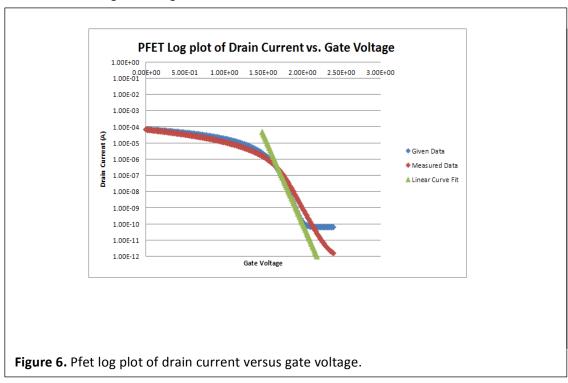

The same procedure up this point was used on a Pfet. To simplify the calculations, the value of the voltage that corresponded with each value of current was subtracted from 2.4 V to obtain curves that resembled those of an Nfet. The same circuit was also used. A below threshold value of kappa was found to be .653. K was found to be 74.24  $\mu$ A/V². An above threshold value of kappa was found to be .90625. The threshold voltage and current were found to be .65 V and 67.1 nA respectively and the thermal voltage was found to be the same as the nfet from before. Figure 7 shows the logarithmic plot of drain current versus gate voltage.

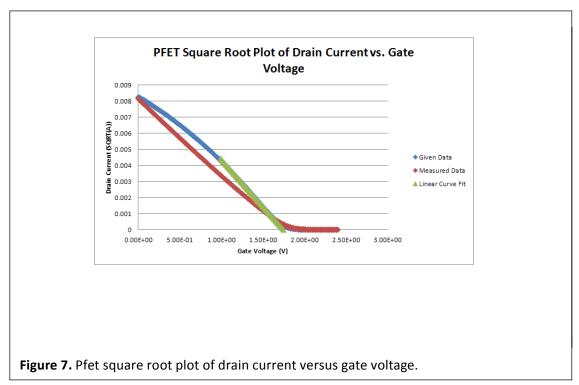

The below threshold region in this plot is adequately simulated by the circuit with the found parameters; however, it begins to deviate at about 1.75 V. The linear region is long enough for the linear curve fit to adequately measure the slope. Figure 7 shows the square root plot of the drain current versus the gate voltage.

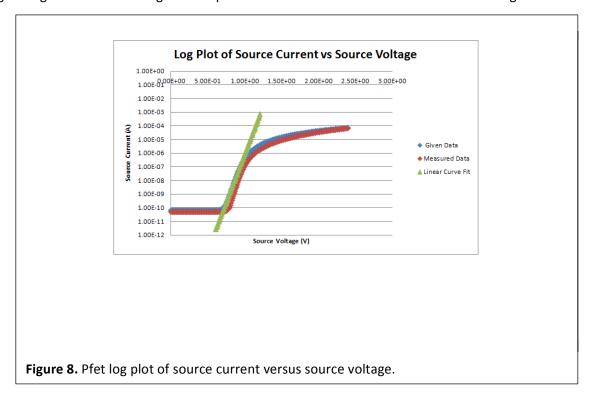

The given data and measured data in figure 7 do line up well in the region past and just before the linear region, but due to the non-linear nature of the given data, the measured data cannot curve to meet the given current measurements. This problem also arises for the linear curve fit trying to fit a non-linear region. Figure 8 shows the logarithmic plot of the source current versus the source voltage.

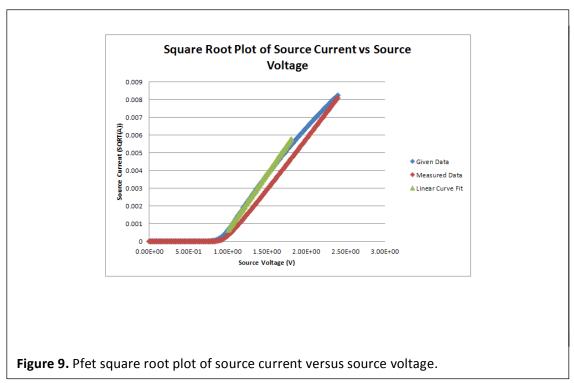

Like the nfet, the source current plots are more accurate than the drain current plots. The plots remain together throughout the entire sweep and the linear curve fit slope is accurate for almost the entire linear region. Figure 9 shows the square root plot of source current versus source voltage.

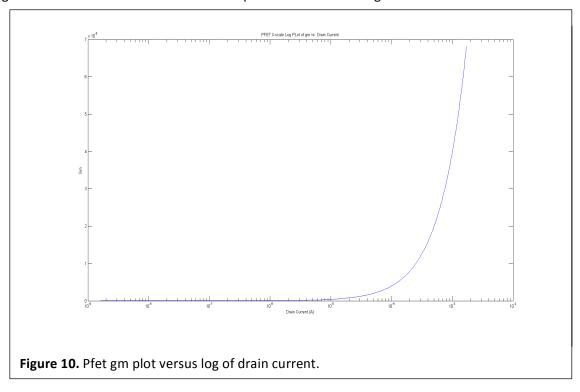

This measured data is close to the given data; however, the K parameter was adjusted to  $60 \,\mu\text{A/V}^2$  and gamma was adjusted to .5 as opposed to being the calculated 1.06. The linear curve fit does give an accurate slope, but only for a section of the linear region and not the entire length. A plot of gm versus a logarithmic current was also taken for the pfet and is shown in figure 10.

## Dependence of Channel Current on Drain Voltage: Tunable Current Source + Early Effect

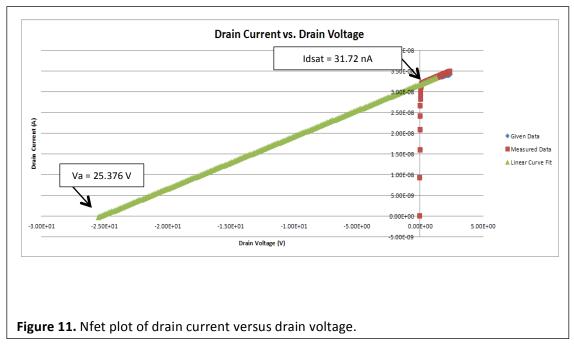

A transistor was biased with a gate voltage of .4 V and a source voltage at ground and was swept with its drain voltage from 0V to 2.4 V. Figure 11 shows the plot of drain current versus drain voltage for an nfet.

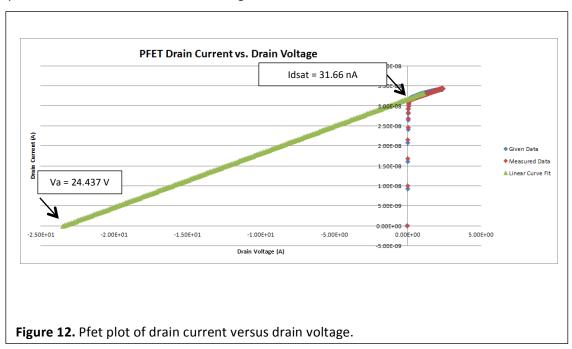

From the linear curve fit extended from the data to the y-axis, it can be seen that the early voltage was found to be 25.376 V. This also corresponds to an Idsat value of 31.72 nA. The measured data also correlates to the given data very well throughout the entire plot. Please note that the value of Lambda was increased to a value of 600. The saturated region of the data occurs after the data levels off and becomes linear. The ohmic region begins before this point. It can also be seen that this data was taken in sub threshold due to the fact that Vds, where the data levels off, is greater than  $4U_T$ . Figure 12 shows the plot of drain current versus drain voltage for a Pfet.

Once again, the measured data lines up with the given data very well only after the value of lambda was adjusted to equal 400. The early voltage for this transistor can be seen from the linear curve fit as being 23.437 V and Idsat has a value of 31.66 nA. This data has the same structure as the nfet in that the saturation region is where the data levels off and the ohmic region is where the data is climbing rapidly. This data was also taken in sub-threshold due to the same reason that Vds, where the data levels off, is greater than  $4U_T$ .